# Filling Narrow Trenches by Iodine-Catalyzed CVD of Copper and Manganese on Manganese Nitride Barrier/Adhesion Layers

Yeung Au, Youbo Lin, and Roy G. Gordon\*,z

Department of Chemistry and Chemical Biology, Harvard University, Cambridge, Massachusetts 02138, USA

We present a process for the void-free filling of sub-100 nm trenches with copper or copper-manganese alloy by chemical vapor deposition (CVD). Conformally deposited manganese nitride serves as an underlayer that initially chemisorbs iodine. CVD of copper or copper-manganese alloy releases the adsorbed iodine atoms from the surface of the manganese nitride, allowing iodine to act as a surfactant catalyst floating on the surface of the growing copper layer. The iodine increases the growth rate of the copper and manganese by an order of magnitude. As the iodine concentrates near the narrowing bottoms of features, void-free, bottom-up filling of CVD of pure copper or copper-manganese alloy is achieved in trenches narrower than 30 nm with aspect ratios up to at least 5:1. The manganese nitride films also show barrier properties against copper diffusion and enhance adhesion between copper and dielectric insulators. During post-deposition annealing, manganese in the alloy diffuses out from copper through the grain boundaries and forms a self-aligned layer that further improves adhesion and barrier properties at the copper/insulator interface. This process provides nanoscale interconnects for microelectronic devices with higher speeds and longer lifetimes.

© 2011 The Electrochemical Society. [DOI: 10.1149/1.3556699] All rights reserved.

Manuscript submitted October 14, 2010; revised manuscript received January 19, 2011. Published March 17, 2011.

The packing density of microelectronic devices has increased exponentially over the past four decades. Continuous enhancements in device performance and functionality have been achieved by scaling of the physical size of devices and increasing the number of wiring levels. With increasing packing density in microelectronic devices, copper (Cu) is used as an interconnecting metal due to its superior electrical conductivity (1.67  $\mu\Omega$  cm) and excellent resistance against electromigration. The dual-damascene process, which involves copper electroplating in preformed trenches and vias in interlayer dielectrics, followed by chemical-mechanical polishing (CMP) of the copper, has been commonly adopted for patterning copper. Compared to vacuum deposition techniques such as chemical vapor deposition (CVD) and physical vapor deposition (PVD), the electroplating process has the ability to fill sub-micrometer trenches and via holes in a bottom-up fashion while avoiding the formation of seams and voids.

Iodine adsorbed on a copper seed layer has been shown to act as a catalytic surfactant to improve growth rate and surface smoothness of copper films deposited by CVD. When Cu(I)-hexafluoroacetylacetonate-vinyltrimethylsilane [Cu(I)(hfac)(vtms)] is used as the precursor, an electronegative iodine atom adsorbed on the copper surface weakens the Cu<sup>+</sup>-(β-diketonate)<sup>-</sup> ionic bond, thus facilitating the dissociation of the precursor molecule and promoting 2D lateral growth. During iodine-catalyzed CVD in sub-micrometer trenches and via holes, the growth rate of copper at the bottom of the features is continuously accelerated due to reduction of surface area and increasing concentration of iodine catalyst. As a result, bottom-up filling of copper could be achieved.<sup>6,7</sup> Modeling of bottom-up filling during iodine-catalyzed CVD was done using the curvature-enhanced accelerator coverage (CEAC) model.<sup>8,9</sup> This catalyst-enhanced process, however, requires a conformal copper seed layer on top of the diffusion barrier and adhesion layer. Preparation of this seed layer is challenging on sub-30 nm features. Moreover, the stack of diffusion barrier, adhesion layer and seed layer will occupy substantial portions of these features, leaving less room for the more conductive copper. The remaining smaller amount of copper has higher resistance and thus slower circuit speeds. The narrower copper wires have a shorter lifetime before the higher current density destroys them by electromigration.

In this paper, we present a process for the bottom-up filling of sub-30 nm trenches with copper or copper-manganese alloy. Iodine is chemisorbed onto the surfaces of a thin, conformal manganese nitride layer that prevents diffusion of copper and also enhances adhesion between copper and the insulating substrates. When CVD of

copper or copper-manganese alloy begins, the iodine is released from the surface of the manganese nitride. The iodine then floats on the surface of a growing copper layer and catalyzes the bottom-up filling of trenches without leaving any seams or voids. Upon post-annealing, manganese in the alloy diffuses out from copper through the grain boundaries and forms a self-aligned layer on nearby insulator surfaces, thereby further improving adhesion and barrier properties at the copper/insulator interface. This process should facilitate the fabrication of future generations of nanoscale microelectronic devices with faster and more robust interconnections.

## Experimental

Patterned substrates with trench structures were obtained with widths around 30–40 nm and aspect ratio of about 5:1. These substrates were cleaned by an oxygen plasma with 10 W RF power at 0.01 Torr pressure for 3 min at room temperature to remove contaminants on the surface and deep in the trenches. Some of the substrates received an additional deposition of silicon dioxide by atomic layer deposition (ALD) to further reduce the widths of the trenches to widths as narrow as 17 nm. <sup>10</sup>

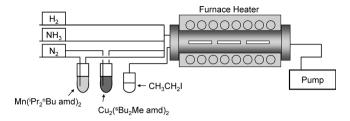

A schematic diagram of the CVD system is shown in Fig. 1. The compound that serves as a precursor for manganese and manganese nitride is called bis(N,N')-diisopropylpentylamidinato) manganese (II), whose chemical formula is shown in Fig. 2. The precursor for copper deposition is a copper (N, N'-di-sec-butylacetamidinate) dimer and has the chemical structure shown in Fig. 3. These compounds were synthesized by methods similar to those described previously. 11,12 To prepare manganese nitride by CVD, the manganese precursor was evaporated from the liquid in a bubbler at a temperature of 90°C into a 60 sccm flow of highly purified nitrogen (concentrations of water and oxygen less than  $10^{-9}$  relative to  $N_2$ ). This vapor mixture was mixed with 60 sccm of purified nitrogen and 60 sccm of purified ammonia (NH<sub>3</sub>) in a tee just before entering one end of a tubular reactor. The reactor tube had an inner diameter of 36 mm. A half-cylinder of aluminum supported the substrates inside the reactor. The reactor temperature was controlled at 130°C and the pressure in the reactor was maintained at 5 Torr by a pressure sensor controlling a butterfly valve between the reactor and the vacuum pump. After deposition of manganese nitride was complete, the substrate was cooled in the reactor in a flow of pure nitrogen in order to protect the manganese nitride film from oxidation. Ethyl iodide (CH3CH2I) was then used as an iodine source to adsorb iodine atoms onto the fresh surface of the manganese nitride film at 50°C. The liquid ethyl iodide was contained in a bubbler at room temperature and its vapor was fed directly into the reactor without a carrier gas, controlled by a needle valve to a pressure of 0.05 Torr. For CVD of copper, the copper precursor was evaporated from the liquid in a bubbler at a temperature of

<sup>\*</sup>Electrochemical Society Active Member.

z E-mail: Gordon@chemistry.harvard.edu

Figure 1. Schematic diagram of the CVD system.

130°C into a 40 sccm flow of highly purified nitrogen. Hydrogen (40 sccm) was mixed with the copper precursor vapor just before entering the reactor held at a temperature of 180°C and a pressure of 5 Torr.

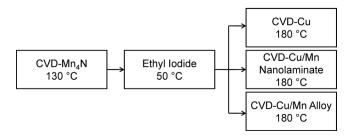

A schematic diagram of the CVD process flow is shown in Fig. 4. In a typical process where the trenches are filled with pure copper, manganese nitride was first deposited at 130°C for 5 min to form 2.5 nm of film. Ethyl iodide was then introduced into the chamber at 50°C for 30 s. CVD copper was deposited at 180°C until the trenches are completely filled, which typically took a few minutes. To fill the trenches with copper-manganese nanolaminate, manganese nitride was first deposited at 130°C for 5 min, followed by an exposure of ethyl iodide at 50°C for 30 s. Copper was then deposited at 180°C for 5 min to form a continuous layer, and ethyl iodide vapors were exposed to the copper surface at 50°C for 30 s. Manganese and copper precursors were then alternately carried into the chamber by 50 sccm of nitrogen and mixed with 50 sccm of hydrogen at a temperature of 180°C and a pressure of 5 Torr. In one cycle, the manganese precursors were supplied for 3 min and the copper precursors were supplied for 5 min. This cycle was repeated until the trenches were completely filled with a coppermanganese nanolaminate. The Mn/Cu ratio was quantified by X-ray fluorescence (XRF). To fill the trenches with copper-manganese alloy, manganese nitride was first deposited at 130°C for 5 min. followed by an exposure of ethyl iodide at 50°C for 30 s. Then the manganese precursor vapors were carried by 60 sccm of nitrogen and simultaneously the Cu precursor vapors were carried by 40 sccm of nitrogen. These precursor vapor flows were mixed together with 100 sccm of hydrogen at a temperature of 180°C and a pressure of 5 Torr.

The thickness of manganese nitride was measured by X-ray reflectometry (XRR), and the thickness of copper was measured by scanning electron microscopy (SEM). Atomic force microscopy (AFM) was used to evaluate the surface morphology of the manganese nitride film. The effectiveness of manganese nitride as a barrier to copper diffusion was tested by looking for its reaction with silicon to form copper silicide under an energy-dispersive X-ray spectrometer (EDX) and SEM. The effectiveness of manganese nitride as an adhesion layer was evaluated by a four-point bend method as described in our previous publication. <sup>13</sup>

Surface analyses and depth profiles of CVD copper on planar PVD Cu seed/thermal SiO<sub>2</sub>/Si substrate were obtained by X-ray

$$H_3C$$

$CH_3$

$H_3C$

$CH_3$

$CH_3$

$CH_3$

$CH_4$

$CH_5$

$CH_6$

$CH_6$

Figure 2. Formula for the Mn precursor.

$$H_3C$$

$CH_3$

$H_3C$

$CH_3$

$CH_3$

Figure 3. Formula for the Cu precursor.

photoelectron spectroscopy (XPS). The effectiveness of CVD copper in super-filling narrow trenches was evaluated by cross sectional SEM and transmission electron microscopy (TEM). The cross sectional SEM and TEM samples were prepared by focused ion beam (FIB).

## **Results and Discussion**

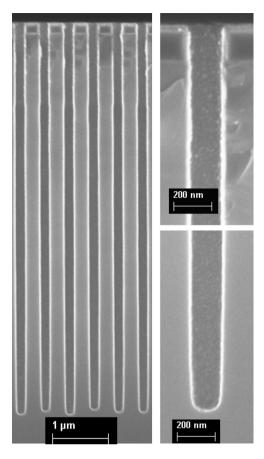

Under the conditions described above, about 2.5 nm of manganese nitride film was deposited in 5 min. At a deposition temperature of  $130^{\circ}C$ , substrates having holes with aspect ratio (ratio of length to diameter) of 52:1 were coated with  $MnN_x$ , x  $\sim 0.25$ . Figure 5 shows a SEM of a cross section through some of these holes. The bright line outlining the holes comes from the  $MnN_x$  film, showing that the material was deposited uniformly and conformally over the inside surfaces of these holes. Electron diffraction showed that the material has the cubic structure known for  $Mn_4N$ .  $^{14}$  AFM showed that  $Mn_4N$  films are fairly smooth, with a root-mean-square roughness equal to 7% of their thickness. The high conformality and smooth morphology allow manganese nitride to be a suitable underlayer to initiate the catalytic CVD processes in deep, narrow trenches

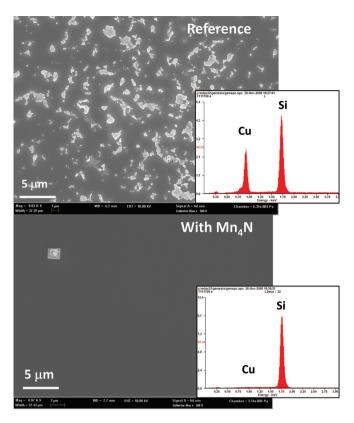

Manganese nitride films show barrier properties against copper diffusion. For this copper diffusion test, 9 nm of SiO<sub>2</sub> were grown on HF-etched silicon wafers by ALD at 250°C, followed by CVD manganese nitride at 130°C for 5 min and a post-deposition anneal at 350°C for 1 h under nitrogen ambient. Control samples of SiO<sub>2</sub> omitted the CVD manganese nitride treatment. Copper layers about 200 nm thick were then deposited on top of the manganese nitride or SiO<sub>2</sub> layers. The samples were then annealed in a pure nitrogen atmosphere at 500°C for 1 h. To see if copper had diffused into the silicon substrate, the copper layers were dissolved in nitric acid, and the manganese nitride and silica were removed by dilute HF. The etched surfaces were then analyzed by an EDX and SEM with the results shown in Fig. 6. The reference sample shows that the majority of its surface is covered by copper silicide crystallites, indicating

Figure 4. Schematic diagram of the CVD process flow.

Figure 5. Step coverage of manganese nitride films in holes with aspect ratio 52:1.

copper has diffused through the thin silica layer. The manganese nitride-treated sample does not show any copper by large-area EDX, showing that Mn<sub>4</sub>N or its reaction product with SiO<sub>2</sub> forms an effective barrier against diffusion of copper.

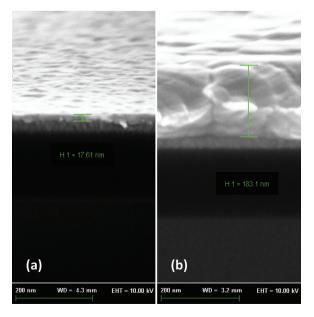

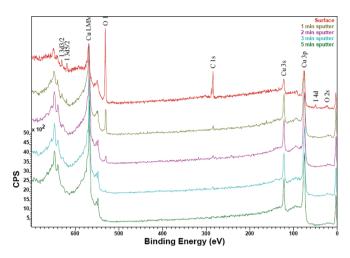

When vapors of ethyl iodide are exposed to copper or manganese nitride underlayers, enhancement in copper growth rate and surface smoothness is observed. On a thin PVD copper seed layer that is not exposed to vapors of ethyl iodide, about 18 nm of copper film is deposited in 1 h at a deposition temperature of 180°C and a pressure of 5 Torr. When vapors of ethyl iodide are exposed to the copper seed layer, about 180 nm of copper film is deposited under the same condition (Fig. 7). The electronegative iodine atom may be weakening the bond between copper and amidinate ligands and facilitating the dissociation of the precursor, resulting in a tenfold accelerated growth rate. XPS depth profile of iodine-catalyzed CVD of copper shows iodine contents only on the top surface of copper (Fig. 8). Signals of iodine disappear together with signals of surface oxygen and carbon as the film is sputtered from the top by argon ions, and no impurities are detectable in the bulk of the copper film. When SiO<sub>2</sub> is exposed to ethyl iodide vapors, no catalytic effects are observed during the CVD process because the bare silica surface is unable to dissociate the ethyl iodide molecule.

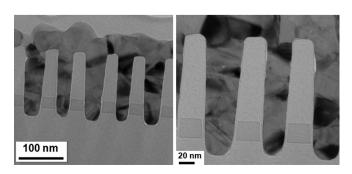

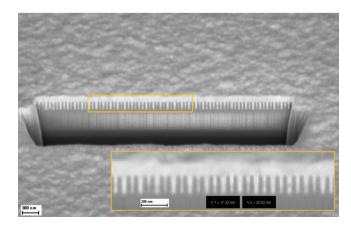

Narrow trenches can be filled by copper in a bottom-up fashion without leaving any voids or seams when a thin manganese nitride film is used as the underlayer and iodine is used as the surfactant catalyst. TEMs in Fig. 9 show that this process completely filled trenches less than 30 nm wide and over 150 nm deep with copper, with an aspect ratio over 5:1. No seams or voids were seen along the centerline of the copper. Wider trenches were partially filled with copper by the same deposition conditions, as shown in Fig. 10. The fact that the copper grew faster from the bottom than from the sides

**Figure 6.** (Color online) SEM and EDX of etched Si surfaces after post-annealing at 500°C for 1 h, indicating manganese nitride is an effective barrier against copper diffusion.

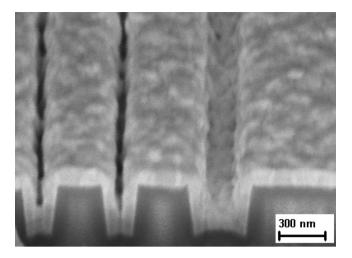

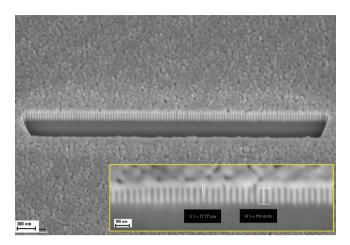

of the trench suggests that iodine pre-adsorbed on the  $Mn_4N$  was released from the  $Mn_4N$  layer and then catalyzed the bottom-up filling of these trenches as a surfactant floating on the growing surface of the copper. Even narrower trenches, with widths as low as 17 nm, depths over 150 nm and aspect ratios as high as 9:1, were also filled with copper by this process, as shown by the SEMs in Figs. 11 and

**Figure 7.** (Color online) Cross sectional SEM showing thickness of CVD Cu film after 1 h of deposition on (a) fresh PVD Cu seed layer, and (b) ethyl iodide-exposed PVD Cu seed layer.

**Figure 8.** (Color online) Depth profile of iodine-catalyzed CVD of Cu, indicating iodine is a surfactant that is not incorporated into the copper film.

12. Some of these high aspect ratio features, however, may contain defects and voids that are unobvious under the SEM. Detailed TEM analyses will be conducted in future studies. One surprising observation from the micrographs in Fig. 9 is that large copper grains completely cross the width of the trenches, even without any post-deposition annealing. This "bamboo structure" is highly desirable, because it extends the lifetimes of copper lines before they fail by electromigration. <sup>15</sup> Another factor that extends the electromigration lifetime is if the adhesion of the copper to the surrounding material is strong. Therefore the adhesion of planar copper films grown on Mn<sub>4</sub>N was tested. Following 2.5 nm of manganese nitride and 70 nm of copper depositions, the structures were annealed at 350°C for one hour in a pure nitrogen gas ambient. Four-point bend tests on these samples showed debonding energies greater than 6.5 J/m², which is a value high enough to survive further fabrication by chemical-mechanical polishing.

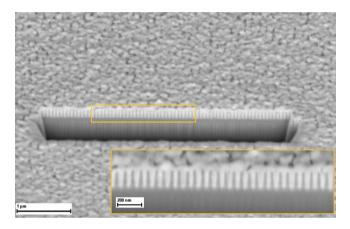

Manganese was incorporated into this CVD copper process to form either a nanolaminate or an alloy which was analyzed by XRF to have approximately 0.5 atom % of manganese in copper. The trenches were once again completely filled with coppermanganese alloy, as shown in Fig. 13. Upon annealing at temperatures above 350°C, manganese will diffuse through the grain boundaries of copper to the surfaces of insulators such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and SiCO low-k insulators. This diffusion process returns the resistivity of copper to its original value and strengthens the copper/dielectric interface by forming a self-aligned barrier and adhesion layer at the interface. When the ratio of manganese to silicon exceeds about 0.5 at the interface between the Cu-Mn and the insulator, the debonding energy becomes larger than about 15 J/m<sup>2</sup>. Such strong interfaces cannot be broken during the four-point bend

**Figure 9.** Cross sectional TEM showing complete filling of narrow trenches by iodine-catalyzed CVD of copper.

Figure 10. Cross sectional SEM showing trenches partly filled by iodinecatalyzed CVD of copper.

test. This very strong adhesion is expected to greatly increase the lifetime of copper interconnects before they fail by electromigration. The amount of manganese in the copper that will be needed to achieve this interfacial concentration will depend on the size and shape of the copper interconnects.

In a substrate with both narrow and wide trenches, the CVD steps may fill the narrow trenches, while conformally coating the wider trenches. Subsequent electroplating can then fill the wider trenches economically. A small amount of iodine (much less than a monolayer) may be attached to the copper surface at the beginning of the electroplating step. There is a possibility that this iodine could dissolve in the copper plating bath and cause corrosion or reliability problems later. Therefore it could be advantageous to remove the iodine from the copper surface prior to plating. Iodine on the surface can be removed by placing the CVD Mn<sub>4</sub>N-CVD Cu substrate into a solution of 30% hydrogen peroxide-70% water for 1 min at room temperature. It was then rinsed in ethanol and deionized water and dried. Examination of the surface by XPS showed that no iodine remained on the surface. Other oxidizing agents, such as sodium hypochlorite, may also be used to remove the iodine from the copper surface. Alternatively, iodine can also be removed by placing the CVD Mn<sub>4</sub>N-CVD Cu substrate in a reactive ion-etch (RIE) system. It was first treated by an oxygen plasma with 150 W microwave power and 50 W RF power at 0.01 Torr pressure for 30 s at room temperature, followed by a hydrogen plasma with 150 W microwave power and 50 W RF power at 0.01 Torr pressure for 3 min at

**Figure 11.** (Color online) Cross sectional SEM showing filling of Cu in narrow trenches (width, ~17 nm) with aspect ratio of 9:1.

**Figure 12.** (Color online) Cross sectional SEM showing filling of Cu in narrow trenches (width, ~18 nm) with aspect ratio of 7:1.

Figure 13. (Color online) Cross sectional SEM showing superfilling of Cu-Mn alloy in trenches with width  $\sim$ 27 nm.

Figure 14. SEM of polyimide plastic coated with Mn<sub>4</sub>N and Cu.

Figure 15. SEM of rough plastic circuit board material coated with  $\mathrm{Mn_4N}$  and  $\mathrm{Cu}$ .

room temperature. It was then rinsed in ethanol and distilled water and dried. No iodine could be detected on the surface by XPS.

This surfactant-catalyzed CVD process can also be extended to metallization of various plastic substrates that are stable up to the deposition temperature of 180°C. Thermally stable polyimide plastic sheet and fiberglass-reinforced circuit boards were selected for this study. After 20 min of manganese nitride deposition, 30 s of ethyl iodide exposure, and 40 min of copper deposition, the surfaces of the plastics were covered by electrically conductive copper films with sheet resistance around 0.5 ohms per square. The smooth surface of a polyimide plastic sheet remained smooth, as shown in Fig. 14. The rough surface of a fiberglass-reinforced circuit board (rootmean-square roughness = 150 nm) was covered conformally, as shown in Fig. 15. The copper adhered strongly to the plastics, and could not be removed by a tape test.

## Conclusion

Narrow trenches, with widths narrower than 30 nm and aspect ratios up to at least 5:1, can be filled with copper or copper-manganese alloy by a CVD method using manganese nitride as an underlayer and iodine as a surfactant catalyst. Copper grows in these trenches in a bottom-up fashion without leaving any voids or seams. The copper grains grow entirely across the widths of the trenches, forming a "bamboo" grain structure that is very resistant to electromigration. Manganese in the alloy diffuses out at elevated temperature and forms a self-aligned barrier and adhesion layer to strengthen the Cu/dielectric interface. Using this bottom-up filling technique, narrow trenches can be completely filled with copper and wider trenches can be coated by a conformal copper-manganese seed layer for electroplating. This CVD process offers a new way to metalize nanoscale interconnects and has the potential to increase the speed and lifetime of copper wires in microelectronics.

## Acknowledgments

The copper and manganese precursors were supplied by the Dow Chemical Company. We appreciate discussions with Hoon Kim. We thank Professor Joost Vlassak for the use of his system for mechanical testing of thin films. This work was performed in part at the Center for Nanoscale Systems (CNS), a member of the National Nanotechnology Infrastructure Network (NNIN), which is supported by the National Science Foundation under NSF award no. ECS-0335765. CNS is part of the Faculty of Arts and Sciences and the School of Engineering and Applied Sciences at Harvard University.

Harvard University assisted in meeting the publication costs of this article.

#### References

- S. P. Murarka, R. J. Gutmann, A. E. Kaloyeros, and W. A. Lanford, *Thin Solid Films*, 236, 257 (1993).

- 2. S. P. Murarka, *Mater. Sci. Eng.*, **R19**, 87 (1997).

- F. B. Kaufman, D. B. Thompson, R. E. Broadie, M. A. Jaso, W. L. Guthrie, D. J. Pearson, and M. B. Small, J. Electrochem. Soc., 138, 3460 (1991).

- P. C. Andricacos, C. Uzoh, J. O. Dukovic, J. Horkans, and H. Deligianni, *IBM J. Res. Dev.*, 42, 567 (1998).

- 5. E. S. Hwang and J. Lee, *Chem. Mater.*, 12, 2076 (2000).

- K. C. Shim, H. B. Lee, O. K. Kwon, H. S. Park, W. Koh, and S. W. Kang, J. Electrochem. Soc., 149, G109 (2002).

- D. Josell, S. Kim, D. Wheeler, T. P. Moffat, and S. G. Pyo, *J. Electrochem. Soc.*, 150, C368 (2003).

- S. G. Pyo, S. Kim, D. Wheeler, T. P. Moffat, and D. Josell, J. Appl. Phys., 93, 1257 (2003).

- D. Josell, D. Wheeler, and T. P. Moffat, *Electrochem. Solid-State Lett.*, 5, C44 (2002).

- 10. D. Hausmann, J. Becker, S. Wang, and R. G. Gordon, Science, 298, 402 (2002).

- 11. B. S. Lim, A. Rahtu, J. S. Park, and R. G. Gordon, *Inorg. Chem.*, 42, 7951 (2003).

- 12. Z. Li, A. Rahtu, and R. G. Gordon, J. Electrochem. Soc., 153, C787 (2006).

- Y. Au, Y. Lin, H. Kim, E. Beh, Y. Liu, and R. G. Gordon, *J. Electrochem. Soc.*, 157, D341 (2010).

- K. Suzuki, T. Kaneko, H. Yoshida, Y. Obi, H. Fujimori, and H. Morita, *J. Alloys Compd.*, 306, 66 (2000).

- 15. D. Kwon, H. Park, and C. Lee, *Thin Solid Films*, 475, 58 (2005).