# Selective Chemical Vapor Deposition of Manganese **Self-Aligned Capping Layer for Cu Interconnections** in Microelectronics

Yeung Au, Youbo Lin, Hoon Kim, Eugene Beh, b Yiqun Liu, and Roy G. Gordon\*,2

Department of Chemistry and Chemical Biology, Harvard University, Cambridge, Massachusetts 02138, USA

In modern Cu interconnections in microelectronics, weak adhesion between the chemical-mechanical polished copper surface and the dielectric capping material can lead to rapid electromigration of Cu and early failure of the wiring. A self-aligned chemical vapor deposition (CVD) Mn capping process is introduced to strengthen the interface between Cu and dielectric insulators without increasing the resistivity of Cu. In this CVD process, a vapor mixture of Mn precursor and molecular hydrogen deposits Mn selectively on copper and not at all on the adjacent, previously deactivated surfaces of insulators. Deactivation of the insulator surfaces is accomplished by exposure to vapors containing reactive alkylsilyl groups. The presence of Mn at the Cu/insulator interface greatly increases the strength of the bonding between Cu and the insulator. The debonding energy increases approximately linearly with the amount of Mn at the interface, up to values so large that the interface could not be broken apart. This Mn-enhanced binding strength of Cu to insulators is observed for all insulators tested, including plasma-enhanced chemical vapor deposited Si<sub>3</sub>N<sub>4</sub>, SiCNOH, SiO<sub>2</sub>, and low-k SiCOH, as well as thermal SiO<sub>2</sub> and atomic-layer-deposited SiO<sub>2</sub>. This selective CVD Mn capping process should increase the lifetime of advanced copper interconnections. © 2010 The Electrochemical Society. [DOI: 10.1149/1.3364799] All rights reserved.

Manuscript submitted November 19, 2009; revised manuscript received February 15, 2010. Published April 26, 2010.

The power of computers has increased exponentially, approximately following Moore's law for the past half a century. This technological feat has been enabled by the fact that transistors improve their performance as they are scaled to smaller and smaller sizes. However, the endurance of the wires (now made of copper) that connect the transistors becomes poorer as their size is reduced. Until now, the performance of the copper wires has been sufficient to meet the industry standard lifetime of 10 years. As the size of the wires is projected to become smaller, their operational lifetime before failure would become too small.

The fundamental problem is that copper metal forms rather weak bonds to metal oxides and nitrides. An adhesive tape is usually sufficient to remove copper films from these surfaces. Quantitative measurements of debonding energy by the four-point bend test usually give values of less than 1 J m<sup>-2</sup>. This poor adhesion between copper and silicon nitride leads to the most common failure mechanisms of copper interconnects in integrated circuits. An open circuit can form when a copper line breaks after an electric current drives copper along the weak interface between copper and an overlying silicon nitride layer. Short circuits between neighboring lines can also form after this electromigration process extrudes copper from the channels in which it lies.

Placing a metal such as cobalt on the top surface of the copper lines increases the lifetime before failure by electromigration. Cobalt or cobalt alloys with tungsten and phosphorus or boron have been placed on copper lines by electroless plating.3 However, avoiding some metal plating on adjacent insulator surfaces has been difficult to achieve, resulting in higher leakage and short circuits between lines. Chemical vapor deposition (CVD) has also been used to deposit Co on Cu lines, but some Co is also deposited on the insulator surfaces, potentially reducing reliability because cobalt on the dielectric can increase leakage and lower the breakdown voltage. Cobalt also diffuses from the capping layer into Cu, increasing its resistance,<sup>5</sup> while manganese can be removed from Cu by annealing.<sup>6</sup> Selective CVD of ruthenium has also been used as a capping layer to increase the lifetime, but some Ru metal is still deposited on the insulator.

Here, we present a process for the selective CVD of manganese

- \* Electrochemical Society Active Member.

- <sup>1</sup> Present address: Applied Materials, Inc., Santa Clara, CA.

<sup>2</sup> Present address: Stanford University, Palo Alto, CA.

- <sup>z</sup> E-mail: Gordon@chemistry.harvard.edu

on the desired surfaces of copper wires while completely avoiding any deposition of manganese on insulators between the copper wires. Gas-phase silvlation is essential to achieving this high degree of selectivity, presumably by replacing reactive SiOH groups on the insulator surface with inert SiCH3 bonds. We also show that manganese metal dramatically strengthens the interface between copper and silicon nitride, as well as between copper and silicon oxide and low-k dielectrics. The debonding energy increases nearly linearly with manganese content at the interface, up to values so large that the interfaces could not be broken apart. Increased adhesion strength has been linked to increased electromigration lifetime. We also evaluated the remarkably high diffusion constant of Mn in polycrystalline copper at 300°C, which helps to understand the distribution of Mn in the samples prepared for the study of adhesion. This selective CVD Mn process should allow the construction of multilevel interconnects with longer lifetime and higher speed than previously possible.

### **Experimental**

The compound that serves as a precursor for the manganese is called bis(N, N'-diisopropylpentanamidinato)manganese(II), whose chemical formula is shown in Fig. 1. The compound was synthesized by methods similar to those used for other metal amidinates. The vapor pressure of the precursor was estimated to be around 0.1 mbar at 90°C. For the CVD experiments, the manganese precursor was evaporated from the liquid in a bubbler at a temperature of  $90^{\circ}$ C into a 60 sccm flow of highly purified nitrogen (concentrations of water and oxygen less than  $10^{-9}$  of  $N_2$ ). This vapor mixture was mixed with 60 sccm of purified hydrogen at a tee just before entering one end of a tubular reactor. The reactor tube had an inner diameter of 36 mm. A half-cylinder of aluminum supported the substrates inside the reactor. For most depositions of manganese, the reactor temperature was controlled at 300°C. The pressure in the reactor was maintained at 5 Torr by a pressure sensor controlling a butterfly valve between the reactor and the vacuum pump.

CVD copper was deposited in the same reactor using copper (N,N'-di-sec-butyl-acetamidinate) dimer<sup>10</sup> as a copper precursor maintained as a liquid in a bubbler at 130°C through which 40 sccm of pure nitrogen flowed. Hydrogen (40 sccm) was mixed with the copper precursor vapor just before entering the reactor held at a temperature of 200°C and a pressure of 5 Torr. Under these conditions, about 30 nm of copper was deposited in 5 min.

Substrates for various measurements are shown schematically in

$$H_3C$$

$CH_3$   $H_3C$   $CH_3$   $CH_3$   $CH_4$   $CH_5$   $CH_5$

**Figure 1.** Formula for the Mn precursor, bis(N, N'-diisopropyl-pentanamidinato) manganese (II).

Fig. 2. They include blanket films of thermal  $SiO_2$  on Si, plasmadeposited  $SiO_2$  on Si,  $CVD\ Si_3N_4$  on Si,  $SiCOH\ low-k$  insulator (BDII, k=2.5, from Applied Materials) on Si, and  $SiCNOH\ capping barrier and etch-stop (BLoK from Applied Materials). Thermal oxide and plasma oxide substrates were cleaned of organic contamination by 5 min of UV-ozone treatment at room temperature. <math>CVD\ silicon\ nitride\ samples\ were\ similarly\ cleaned\ by\ UV\ ozone,\ then dipped in dilute HF for 1 min, rinsed with distilled water, and blown dry. BDII and BLoK samples were used as received without any cleaning. Blanket copper substrates were either evaporated or sputtered onto thermally oxidized silicon wafers. A layer of titanium was sputtered before copper to provide stronger adhesion to the sputtered copper films. The copper substrates were loaded into the CVD reactor after only a few minutes of air break, so they were fairly clean, except for a thin layer of native oxide.$

Patterned substrates with interdigitated comb structures were supplied by IBM and by SELETE. These substrates had copper lines up to 10 m long with 50, 70, or 100 nm copper linewidths separated by dense SiCOH insulators with the same linewidths. These substrates received a final step of chemical-mechanical polishing, leaving the copper surfaces covered by a protective layer of benzotriazole (BTA). These patterned substrates were not cleaned before use.

After the substrates were loaded into the reactor, they were flushed with purified nitrogen while they were heated to 200°C for 0.5 h and 350°C for 0.25 h in flowing purified nitrogen at 1 Torr. During this time, water was desorbed from the dielectrics and the BTA was evaporated from the copper. Next, the native oxide on the copper surfaces was reduced in flowing purified hydrogen gas at 1 Torr for 1 h at 250°C. In some runs, manganese was deposited at this point. In most runs, two silylation vapor pretreatments were applied before the manganese deposition. <sup>11,12</sup> Before the silylation

|                          | 7                                                                |                                                              |

|--------------------------|------------------------------------------------------------------|--------------------------------------------------------------|

| CVD Mn                   | ALD SiO <sub>2</sub>                                             | CVD Mn                                                       |

| PVD Cu                   | CVD Mn                                                           | PECVD SiO <sub>2</sub> or SiCOH                              |

| PVD Ti                   | PVD Cu                                                           | Si                                                           |

| Thermal SiO <sub>2</sub> | Thermal SiO <sub>2</sub>                                         | (c)                                                          |

| Si                       | Si                                                               | Si                                                           |

| (a)                      | (b)                                                              | Ероху                                                        |

|                          | Si                                                               | PVD AI                                                       |

|                          | 31                                                               | FVDAI                                                        |

|                          | Ероху                                                            | PECVD Si <sub>3</sub> N <sub>4</sub> or ALD SiO <sub>2</sub> |

|                          | PVD AI                                                           | CVD Cu                                                       |

| CVD Cu                   | CVD Cu                                                           | CVD Mn                                                       |

| CVD Mn                   | CVD Mn                                                           | PVD Cu                                                       |

| CVD Cu                   | CVD Cu                                                           | PVD Ti                                                       |

| Thermal SiO <sub>2</sub> | SiO <sub>2</sub> , SiCOH, SiCNOH, Si <sub>3</sub> N <sub>4</sub> | SiO <sub>2</sub>                                             |

| Si                       | Si                                                               | Si                                                           |

| (d)                      | (e)                                                              | (f)                                                          |

**Figure 2.** Structures of samples for measuring CVD manganese (a) deposition rate and diffusion rate, (b) SIMS depth profile, (c) selectivity, (d) purity, (e) adhesion to substrates, and (f) adhesion to superstrates.

treatments, the reactor was cooled to room temperature, pumped down to the base pressure (about 20 mTorr), and then filled with vapor (about 14 Torr) from a room-temperature source of bis(N, N-dimethylamino)dimethylsilane  $[(CH_3)_2Si[N(CH_3)_2]_2]$  and heated to 90°C for 0.5 h. Then, the reactor was again pumped to base pressure, cooled to room temperature, and refilled with the vapor (about 75 Torr) of (N,N-dimethylamino)trimethylsilane [(CH<sub>3</sub>)<sub>3</sub>SiN(CH<sub>3</sub>)<sub>2</sub>] and heated to 90°C for 0.5 h. The samples were then heated to the deposition temperature (typically, 300°C for manganese or 200°C for copper). After the temperature was stabilized, a CVD vapor mixture was passed through the reactor for a time, typically 30 min. Some depositions were just manganese, while other runs deposited copper, then manganese, and then a second copper deposition to make Cu/Mn/Cu sandwich structures. Samples for measuring the adhesion of Cu/Mn/Cu to the substrate by the four-point bend method <sup>13-15</sup> were taken through an air break into a chamber in which they received 0.13 µm of sputtered aluminum, and then they were attached by high strength epoxy (EPO-TEK 353ND from Epoxy Technology) to a piece of a second silicon wafer. The bonded wafers were cut into 50 × 6 mm beams. A notch was scribed at the center on one of the substrates to initiate the crack. Samples for testing the adhesion of copper-manganese to a superstrate silicon nitride layer received an additional plasma-enhanced chemical vapor deposited Si<sub>3</sub>N<sub>4</sub> or atomic-layer-deposited SiO<sub>2</sub> coating before the sputtered aluminum.

Rutherford backscattering (RBS) was used to measure quantitatively the amount of manganese deposited on various substrates. The detection limit for manganese on substrates containing the elements silicon, oxygen, nitrogen, hydrogen, and carbon is very low, <5  $\times$  10<sup>13</sup> cm<sup>-2</sup>, because there is no background signal from these light elements. On thick copper layers, a large background could obscure the manganese RBS signal. Therefore, thin copper films (10-20 nm thick) were used as substrates for the RBS analysis of Mn/Cu, so that the manganese and copper peaks could be resolved. X-ray photoelectron spectroscopy (XPS) was also used for semiquantitative analysis of the films. XPS and secondary-ion mass spectrometry (SIMS) were used for studying the depth distribution of the elements. Transmission electron microscopy (TEM) was also used to study the structure of the deposited material. Test comb structures supplied by our industrial collaborators were used to measure the leakage current between copper lines as well as the resistance along the copper lines before and after the CVD of manganese. Two types of dielectric capping layer insulators, silica and silicon nitride, were applied to these structures after the CVD of Mn. SiO<sub>2</sub> (20 nm) was deposited by atomic layer deposition (ALD) at 250°C, 16 or Si<sub>3</sub>N<sub>4</sub> (17 nm) was deposited by plasma-enhanced chemical vapor deposition (PECVD) at 300°C. Electrical measurements of leakage and resistance before and after the Mn capping layer deposition were carried out with an HP 4275A meter in a shielded probe station at room temperature.

## **Results and Discussion**

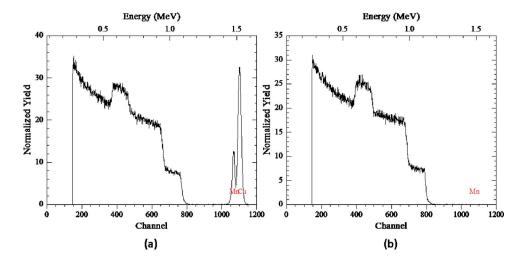

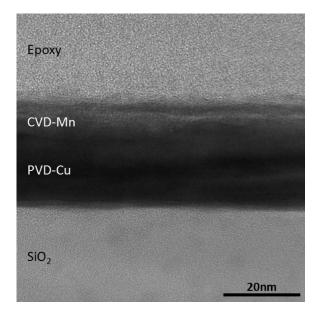

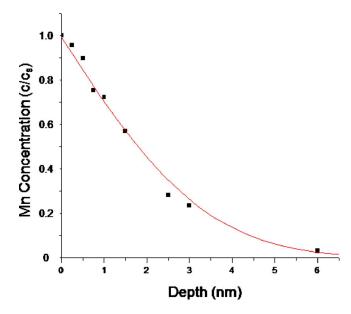

A manganese film was deposited on 20 nm Cu for 30 min. The RBS data shown in Fig. 3a for this film correspond to 6.75  $\times$  10<sup>16</sup> Mn atom cm<sup>-2</sup>, or 8 nm, if this material had the normal density of bulk manganese. A cross-sectional TEM image of this film is shown in Fig. 4. Cu appears slightly darker than Mn because its electron density is about 25% higher than that of Mn. The boundary between Mn and Cu is not sharp because Mn has partly diffused into the Cu. To study this diffusion process more carefully, Mn was deposited onto a thicker Cu layer for 20 min without H<sub>2</sub>, resulting in about 10<sup>16</sup> Mn atom cm<sup>-2</sup>. The surface composition of this sample was determined by XPS to be about 1/3 Mn and 2/3 Cu. Sputtering this sample under  $3.8 \times 10^{-7}$  Torr of argon atmosphere provided the depth distribution of Mn, as shown in Fig. 5. The line is the solution to Fick's second law of diffusion on the assumption that the surface concentration of Mn remains constant during the CVD process, and that diffusion is then guenched by cooling after the deposition is complete. The diffusion constant determined from this fit is

**Figure 3.** (Color online) RBS of CVD manganese on silylated (a) copper and (b) SiO<sub>2</sub>.

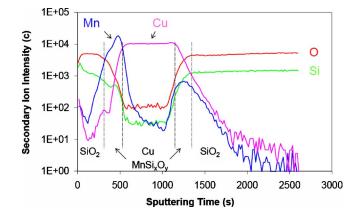

$3\times10^{-21}~\text{m}^2~\text{s}^{-1},$  although this value may be slightly too high because of ion mixing during the depth profiling and because of the penetration depth ( $\sim1~\text{nm})$  of the XPS analysis. This estimated value is about 30 times larger than the value reported for the diffusion of Mn into single-crystal Cu at 300°C.  $^{17}$  Presumably, the higher diffusion rate observed in our sample is due to the rapid diffusion of Mn along grain boundaries in the polycrystalline sputtered Cu layer. A sample was prepared for the SIMS depth profile shown in Fig. 6. Manganese was deposited on 20 nm of Cu, followed by a postanneal at 350°C to diffuse Mn into the Cu layer. Then SiO2 (20 nm) was deposited by ALD on top of the Mn/Cu alloy. The sample was then annealed at 400°C for 2 h to allow Mn to diffuse out from Cu. The depth distribution confirms the diffusion of Mn through Cu to form manganese silicate (MnSixOy) at the Cu/SiO2 interfaces.  $^6$

The purity of the deposited manganese was determined by depositing CVD Cu, then CVD Mn, and then CVD Cu again without removing the substrate from the reactor. This structure protects Mn from contamination by elements such as carbon and oxygen from the ambient atmosphere. This surface contamination is confined to the surface of the outer Cu layer, which is removed by the initial sputtering during the XPS analysis. No carbon, nitrogen, or oxygen impurities were found within the Cu/Mn/Cu layers at the level of sensitivity of XPS,  $\sim 1\%$ .

Figure 4. Cross-sectional TEM of CVD Mn on physical vapor deposited Cu.

The effect of manganese concentration on the adhesion strength of copper-manganese alloys to various insulators was tested by the

**Figure 5.** (Color online) Distribution of Mn in Cu after CVD ( $c_s$  is the surface concentration). Squares are the XPS measurements and the line is calculated for diffusion from a constant surface concentration.

Figure 6. (Color online) SIMS depth profile of  $\rm SiO_2/Mn/Cu/SiO_2$  structure after postannealing at  $400^{\circ}\rm C.$

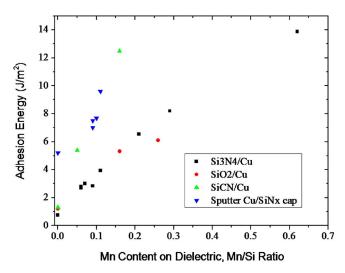

**Figure 7.** (Color online) Adhesion energy of Cu(Mn) vs Mn/Si ratio on the surface of the dielectric. All Cu films were made by CVD except for sputtered Cu under the PECVD  $SiN_x$  cap.

four-point bend method. Various thicknesses (10-50 nm) of the Cu and Mn layers were chosen so that the amount of Mn diffusing through the copper to the copper/insulator interfaces of the Cu/ Mn/Cu layers could be varied widely. The top Cu layer is necessary to protect Mn from oxidation during the air break between CVD Mn and PECVD Si<sub>3</sub>N<sub>4</sub>. After the debonding test, the fracture surfaces were analyzed by XPS to determine which interface had cracked apart. On debonded insulator surfaces, the ratio of Mn to Si was estimated from the XPS data. The resulting interface fracture energies between copper and the insulator are plotted in Fig. 7 as a function of the Mn/Si ratio on the insulator surface from the fractured interface. When no Mn is present at the interface, pure Cu is detached very easily from the surface of the insulating substrates, with interface fracture energy 0.7 J m<sup>-2</sup> for Si<sub>3</sub>N<sub>4</sub> and about 1.2 J m<sup>-2</sup> for SiO<sub>2</sub> or SiCNOH. These pure Cu films are easily removed from the insulators with adhesive tape. Cu films through which Mn diffused to the insulator surface adhere much more strongly, and they cannot be removed by tape. The interface fracture energy increases nearly linearly with the amount of Mn at the interface, to very high values over 10 J m<sup>-2</sup>. Samples were also prepared under conditions (longer Mn deposition times, thinner Cu layers) that should provide more Mn at the interface than those samples that were plotted in Fig. 7. However, these higher Mn interfaces were so strongly bonded together that they could not be broken apart, so specific interface energies could not be determined for them. Instead, these samples debonded at the Al/epoxy interface with a measured fracture toughness of more than 30 J m<sup>-2</sup>. Mn/Si values could not be measured for these very strongly bonded interfaces because we do not have access to a free debonded interface for surface analysis.

Manganese was also found to increase the adhesion of silicon nitride deposited on top of copper. First, CVD manganese and then CVD Cu were applied to sputtered Cu/Ti/SiO $_2$ /Si substrates. After an air break, this surface was cleaned by ammonia plasma, and 300 nm of Si $_3$ N $_4$  was applied by PECVD, followed by 0.13  $\mu m$  of sputtered aluminum. The resulting debonding energies in Fig. 7 show that the addition of Mn/Si = 0.1 also strengthens the adhesion of PECVD Si $_3$ N $_4$  deposited on top of copper to about 10 J m $^{-2}$ . Si $_3$ N $_4$ /Mn/Cu interfaces having Mn/Si ratios larger than 0.1 could not be broken apart.

When insulator surfaces were used as substrates for CVD Mn, much less Mn is deposited than on copper substrates. For thermal  ${\rm SiO_2}$  substrates, about  $1.93\times 10^{15}$  cm<sup>-2</sup> Mn atoms were found, which is 35 times less Mn than is deposited on Cu under the same

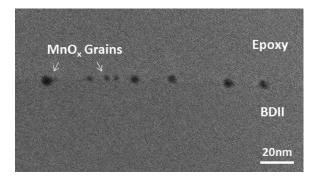

Figure 8. Cross-sectional TEM of CVD Mn on unpassivated low-k dielectric, BDII.

conditions. Similar results were found for a low-k insulator (Applied Materials BDII, dielectric constant 2.5), on which 1.79  $\times$  10<sup>15</sup> cm<sup>-2</sup> Mn atoms were measured, or 38 times less Mn than deposited on Cu. To understand this selectivity better, a cross-sectional TEM image was taken of this sample (Fig. 8). Mn nuclei are seen scattered on the surface, but no continuous layer of Mn has formed. Evidently, most of the insulator surface is not reactive to the Mn precursor in the presence of hydrogen, so growth takes place only on a few reactive sites on the surface. This result is in surprising contrast to the uniform layer of manganese silicate formed on the surface of silica by the same manganese precursor in the absence of hydrogen.

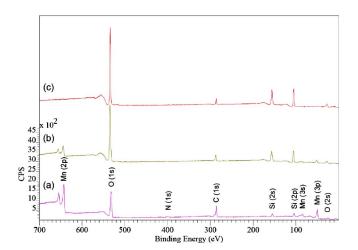

To prevent growth on these reactive sites, we prereacted them with silylamides that can replace these sites with Si-methyl bonds, which are notably unreactive. As the first step in this passivation process, the vapor of (CH<sub>3</sub>)<sub>2</sub>Si[N(CH<sub>3</sub>)<sub>2</sub>]<sub>2</sub> was reacted with the insulator surfaces because it reacts with pairs of neighboring SiOH groups, as well as with isolated SiOH groups. A vapor of (CH<sub>3</sub>)<sub>3</sub>SiN(CH<sub>3</sub>)<sub>2</sub> was then applied because this compound reacts with any remaining isolated SiOH bonds. Successive application of these two treatments was found to completely inhibit the growth of CVD manganese on the treated insulator surfaces even after 30 min of Mn deposition. RBS found no Mn at all on any of the insulator surfaces, with a detection limit of  $< 5 \times 10^{13}$  Mn atom cm<sup>-2</sup> (Fig. 3b). This limit is less than 0.07% of the amount of Mn deposited on Cu under the same conditions, or a selectivity of at least 1300:1. This high selectivity was confirmed by XPS, which could not detect any Mn on the treated insulator surfaces. If only one of the silylation treatments was applied, then residual Mn was detected by RBS and XPS (Fig. 9) on insulator surfaces after CVD Mn. Thus, the combination of the two treatments is much more effective in deactivating the surface than either one applied individually.

To study the effect of these two silylation treatments on Cu surfaces, air-exposed Cu films were exposed to the two silylamide vapors. The XPS analysis of the treated surface showed the presence of silicon. Thus, copper oxide does have sites, probably CuOH bonds, that are reactive to the silylamides. To remove these reactive sites from Cu, air-exposed Cu was heated to 250°C in a flow of hydrogen gas for 1 h, cooled down to room temperature in the reactor, and then exposed in sequence to the two silylamides without any intervening air exposure. The resulting copper surface was free of silicon, according to XPS analysis. We conclude that a clean copper surface does not react with the silylamide vapors.

Test comb structures with interdigitated copper lines and insulators were also used as substrates for Mn deposition. After drying, reduction, and silylation as described above, the reactor was heated to 300°C and the Mn precursor vapor and hydrogen were applied together for 20 min. The reactor was cooled down to room temperature before removing the samples for electrical testing. Samples were then transferred to other reactors for capping by PECVD Si<sub>3</sub>N<sub>4</sub> or by ALD SiO<sub>2</sub>. <sup>16</sup>

Figure 9. (Color online) XPS showing the effectiveness of self-assembled monolayer treatments on surface passivation (a) (CH<sub>3</sub>)<sub>3</sub>SiN(CH<sub>3</sub>)<sub>2</sub> only, (b)  $(CH_3)_2Si[N(CH_3)_2]_2$  only, and (c)  $(CH_3)_2Si[N(CH_3)_2]_2$  followed by (CH<sub>3</sub>)<sub>3</sub>SiN(CH<sub>3</sub>)<sub>2</sub>.

Line-to-line leakage current remained unchanged by Mn deposition on these patterned substrates. Resistance along a line increased by 1-4% after Mn deposition, but then decreased by 9-12% after an anneal at 400°C for 1 h. During this anneal process, the manganese diffuses out of the Cu and forms a manganese silicate layer within the surface of nearby silica surfaces and forms direct Cu-to-Cu contact between levels without any intervening Mn. <sup>19</sup> The final resistivity is lower than the starting value because of copper grain growth during the anneal. Manganese silicate has been shown to be an excellent barrier to the diffusion of copper<sup>20</sup> as well as to water and oxygen. Thus, Cu wiring could be capped by silica-based low-k dielectrics instead of the currently used silicon nitride, which has a much higher dielectric constant. This replacement would lower the overall dielectric constant of the interconnect structure, and thus increase its speed of operation.

#### **Conclusions**

The presence of manganese metal at the interface between copper and insulators is shown to increase the adhesion strength dramatically. The debonding energy increases approximately linearly with the amount of manganese at the interface. A selective CVD process was developed to deposit the manganese only on copper surfaces while completely avoiding any deposition on adjacent silylated surfaces of insulators, such as silica or silicon-oxygen-carbon low-k dielectrics. This selective CVD process has the potential to increase the lifetime of copper wires in microelectronics without any increase in resistance due to the capping metal between levels of interconnects. At the same time, the process can reduce the capacitance and increase the speed of interconnects by eliminating the need for a high-k diffusion barrier on top of each level of wiring.

#### Acknowledgments

The copper precursor was supplied by Dow Chemical Co. Substrates were supplied by IBM, SELETE, and Applied Materials. The SIMS spectrum was provided by IBM. We appreciate discussions with Harish Bhandari. We thank Professor Joost Vlassak for the use of his system for mechanical testing of thin films. This work was performed in part at the Center for Nanoscale Systems (CNS), a member of the National Nanotechnology Infrastructure Network (NNIN), which is supported by the National Science Foundation under NSF award no. ECS-0335765. CNS is part of the Faculty of Arts and Sciences at Harvard University.

Harvard University assisted in meeting the publication costs of this article.

#### References

- C. S. Hau-Riege, Microelectron. Reliab., 44, 195 (2004)

- C.-K. Hu, L. M. Gignac, E. Liniger, C. Detavernier, S. G. Malhotra, and A. Simon, J. Appl. Phys., 98, 124501 (2005).

- P. Singer, Semicond. Int., http://www.semiconductor.net/article/199242 (2005). E. Nakazawa, K. Arita, Y. Tsuchiya, Y. Kakuhara, S. Yokogawa, T. Kurokawa, N. Sasaki, S. Ganguli, H. C. Ha, W. T. Lee, et al., in Advanced Metallization Conference 2008 XXIV, p. 419 (2008).

- C.-K. Hu, L. Gignac, and R. Rosenberg, Microelectron. Reliab., 46, 213 (2006).

- J. Iijima, Y. Fujii, K. Neishi, and J. Koike, J. Vac. Sci. Technol. B, 27, 1963 (2009).

- K. Suzuki, U.S. Pat. Appl. 2009/0065939 (2009).

- M. W. Lane, E. G. Liniger, and J. R. Lloyd, J. Appl. Phys., 93, 1417 (2003).

- B. S. Lim, A. Rahtu, J.-S. Park, and R. G. Gordon, *Inorg. Chem.*, 42, 7951 (2003).

Z. Li, S. T. Barry, and R. G. Gordon, *Inorg. Chem.*, 44, 1728 (2005).

- 11. F. Deyhimi and J. A. Coles, Helv. Chim. Acta, 65, 1752 (1982).

- 12. J. Farkas, M. J. Hampden-Smith, and T. T. Kodas, J. Electrochem. Soc., 141, 3547

- 13. R. H. Dauskardt, M. Lane, Q. Ma, and N. Krishna, Eng. Fract. Mech., 61, 141 (1998).

- 14. M. Lane and R. H. Dauskardt, J. Mater. Res., 15, 2758 (2000).

- Y. Lin, J. J. Vlassak, T. Y. Tsui, and A. J. McKerrow, Mater. Res. Soc. Symp. Proc.,

- 16. D. Hausmann, J. Becker, S. Wang, and R. G. Gordon, Science, 298, 402 (2002).

- A. Almazouzi, M.-P. Macht, V. Naundorf, and G. Neumann, Phys. Status Solidi A, **167**, 15 (1998).

- R. G. Gordon, H. Kim, Y. Au, H. Wang, H. Bhandari, Y. Liu, D. K. Lee, and Y. Lin, in Advanced Metallization Conference 2008 XXIV, p. 321 (2008)

- M. Haneda, J. Iijima, and J. Koike, Appl. Phys. Lett., 90, 252107 (2007).

J. Koike, M. Haneda, J. Iijima, and M. Wada, in IEEE International Interconnect Technology Conference, IEEE, p. 161 (2006).