#### HARVARD UNIVERSITY Graduate School of Arts and Sciences

#### DISSERTATION ACCEPTANCE CERTIFICATE

The undersigned, appointed by the

Department of Chemistry & Chemical Biology

have examined a dissertation entitled:

#### Chemical Vapor Deposition of Thin Film Materials for Copper Interconnects in Microelectronics

presented by : Yeung Au

candidate for the degree of Doctor of Philosophy and hereby certify that it is worthy of acceptance.

Signature Typed name: Prof. Roy G. Gordon Signature Typed name: Prof. Ted Betley Signature Typed name: Prof. Joost Vlassak

Date: 03 May 2012

## Chemical Vapor Deposition of Thin Film Materials for Copper Interconnects in Microelectronics

A dissertation presented

by

Yeung Au

to

#### The Department of Chemistry and Chemical Biology

in partial fulfillment of the requirements

for the degree of

#### **Doctor of Philosophy**

in the subject of

Chemistry

Harvard University Cambridge, Massachusetts May, 2012

© 2012 – Yeung Au

All rights reserved.

# Chemical Vapor Deposition of Thin Film Materials for Copper Interconnects in Microelectronics

#### Abstract

The packing density of microelectronic devices has increased exponentially over the past four decades. Continuous enhancements in device performance and functionality have been achieved by the introduction of new materials and fabrication techniques. This thesis summarizes the thin film materials and metallization processes by chemical vapor deposition (CVD) developed during my graduate study with Professor Gordon at Harvard University. These materials and processes have the potential to build future generations of microelectronic devices with higher speeds and longer lifetimes.

**Manganese Silicate Diffusion Barrier**: Highly conformal, amorphous and insulating manganese silicate ( $MnSi_xO_y$ ) layers are formed along the walls of trenches in interconnects by CVD using a manganese amidinate precursor vapor that reacts with the surfaces of the insulators. These  $MnSi_xO_y$  layers are excellent barriers to diffusion of copper, oxygen and water.

**Manganese Capping Layer**: A selective CVD manganese capping process strengthens the interface between copper and dielectric insulators to improve the electromigration reliability of the interconnects. High selectivity is achieved by deactivating the insulator surfaces using vapors

containing reactive methylsilyl groups. Manganese at the Cu/insulator interface greatly increases the strength of adhesion between the copper and the insulator.

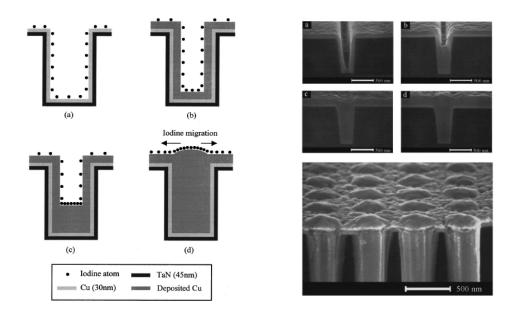

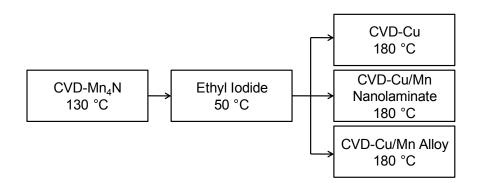

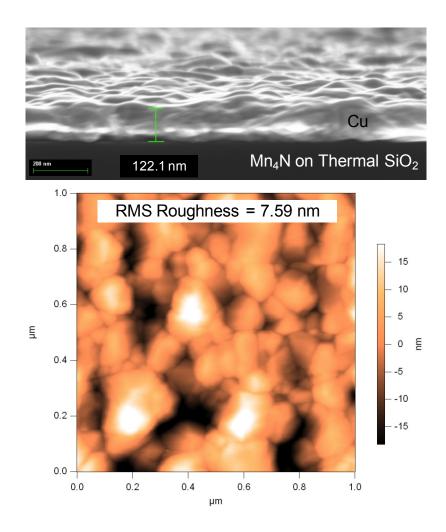

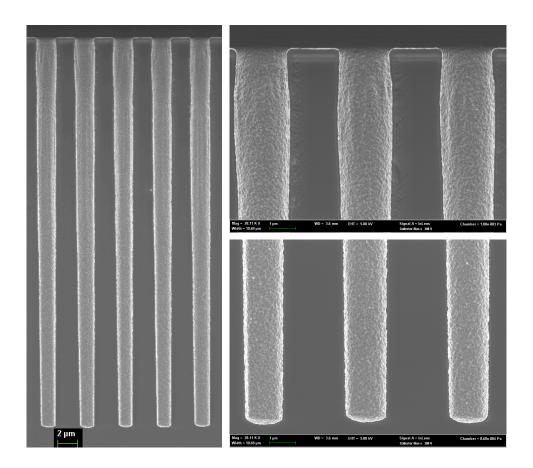

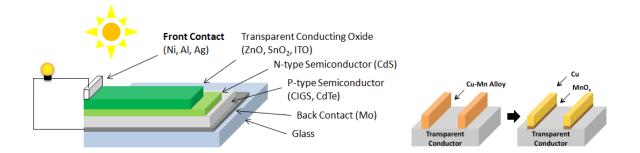

**Bottom-up Filling of Copper and Alloy in Narrow Features:** Narrow trenches, with widths narrow than 30 nm and aspect ratios up to 9:1, can be filled with copper or copper-manganese alloy in a bottom-up fashion using a surfactant-catalyzed CVD process. A conformal manganese nitride (Mn<sub>4</sub>N) layer serves as a diffusion barrier and adhesion layer. Iodine atoms chemisorb on the Mn<sub>4</sub>N layer and are then released to act as a catalytic surfactant on the surface of the growing copper layer to achieve void-free, bottom-up filling. Upon post-annealing, manganese in the alloy diffuses out from the copper and forms a self-aligned barrier in the surface of the insulator.

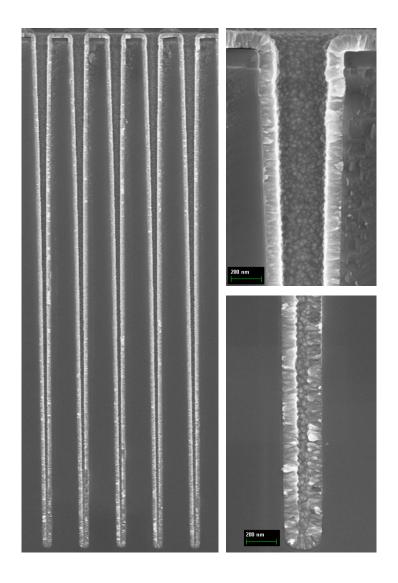

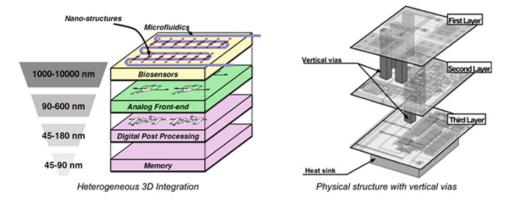

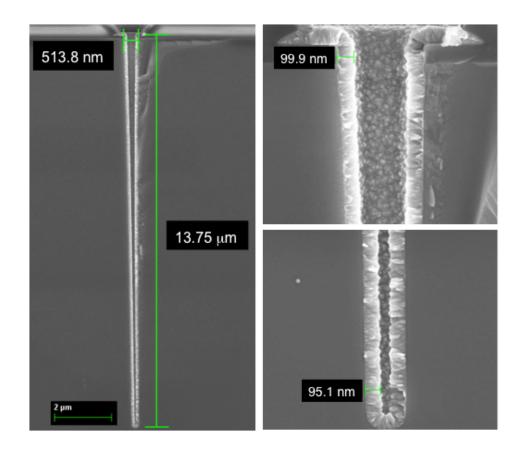

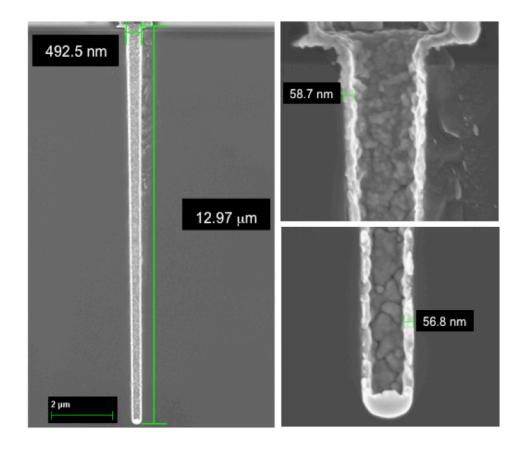

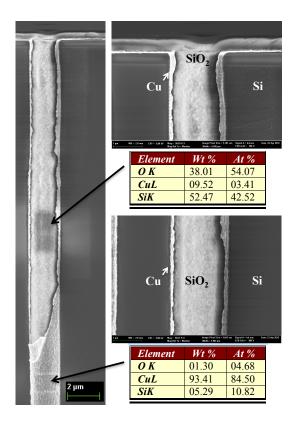

**Conformal Seed Layers for Plating Through-Silicon Vias:** Through-silicon vias (TSV) will speed up interconnections between chips. Conformal, smooth and continuous seed layers in TSV holes with aspect ratios greater than 25:1 can be prepared using vapor deposition techniques. Mn<sub>4</sub>N is deposited conformally on the silica surface by CVD to provide strong adhesion at Cu/insulator interface. Conformal copper or Cu-Mn alloy seed layers are then deposited by an iodine-catalyzed direct-liquid-injection (DLI) CVD process.

### **Table of Contents**

| Abstract                                     | iii |

|----------------------------------------------|-----|

| Table of Contents                            | v   |

| Acknowledgements                             | ix  |

|                                              |     |

| Chapter 1. Introduction                      | 1   |

| 1.1 Copper Interconnects in Microelectronics | 2   |

| Device Scaling and RC Delay                  | 2   |

| Low-k Dielectric Materials                   |     |

| Copper Interconnects                         | 4   |

| Diffusion Barriers                           | 5   |

| Seed Layers                                  | 6   |

| The Damascene Process                        | 7   |

| Electromigration Reliability                 | 8   |

| 1.2 Deposition Techniques                    |     |

| Physical Vapor Deposition                    |     |

| Chemical Vapor Deposition                    | 11  |

| First Order Model of Deposition              | 13  |

| 1.3 Characterization of Thin Films           | 16  |

| Thickness and Structural Characterization    |     |

| Chemical Characterization                    |     |

| Adhesion Test                                |     |

| References                                   | 21  |

| Chapter 2. Chemical Vapor Deposition of Manganese Silicate Diffusion Barrier | 23   |

|------------------------------------------------------------------------------|------|

| 2.1 Introduction                                                             | 23   |

| 2.2 Experiments                                                              | 25   |

| Metal Amidinate Precursors                                                   | 25   |

| CVD Reactor Setup and Characterization Methods                               | 27   |

| 2.3 Results and Discussion                                                   | 28   |

| Formation of Manganese Silicate                                              | . 28 |

| Copper Diffusion Barrier Tests                                               | 29   |

| Oxygen Barrier Tests                                                         | 32   |

| Adhesion Enhancement                                                         | 34   |

| 2.4 Conclusions                                                              | 35   |

| References                                                                   | 37   |

| Chapter 3. Selective Chemical Vapor Deposition of Manganese Capping Layer | 38 |

|---------------------------------------------------------------------------|----|

| 3.1 Introduction                                                          |    |

| 3.2 Experiments                                                           | 40 |

| Structure of Samples for Measurements                                     | 40 |

| CVD of Manganese and Copper                                               | 41 |

| Characterization Methods                                                  | 43 |

| 3.3 Results and Discussion                                                | 45 |

| Diffusion of Manganese in Polycrystalline Copper                          | 45 |

| Adhesion Enhancement at Copper/Capping Layer Interface                    | 48 |

| Selective Deposition of Manganese                                         | 49 |

| Line-to-line Leakage Measurements                                            | 53         |

|------------------------------------------------------------------------------|------------|

| 3.4 Conclusions.                                                             | 55         |

| References                                                                   | 56         |

|                                                                              |            |

| Chapter 4. Surfactant-catalyzed Bottom-up Filling of Copper and Copper-manga | nese Alloy |

| in Narrow Features                                                           | 58         |

| 4.1 Introduction                                                             | 58         |

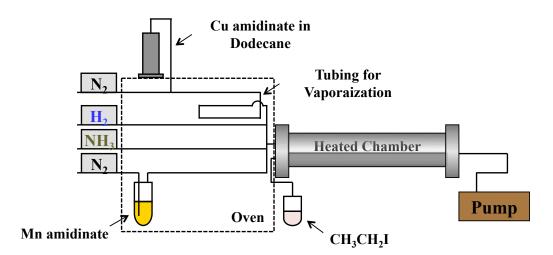

| 4.2 Experiments                                                              | 60         |

| Deposition of Manganese Nitride, Copper, and Copper-manganese                |            |

| Alloy Films                                                                  | 60         |

| Characterization Methods                                                     | 63         |

| 4.3 Results and Discussion.                                                  | 64         |

| Conformal Deposition of Manganese Nitride Films                              | 64         |

| Barrier and Adhesion Properties of Manganese Nitride Films                   | 65         |

| Surfactant-catalyzed CVD of Copper                                           | 67         |

| Bottom-up Filling of Narrow Trenches by Surfactant-catalyzed                 |            |

| CVD of Copper                                                                | 68         |

| Bottom-up Filling of Narrow Trenches by Surfactant-catalyzed                 |            |

| CVD of Cu-Mn Alloy                                                           | 70         |

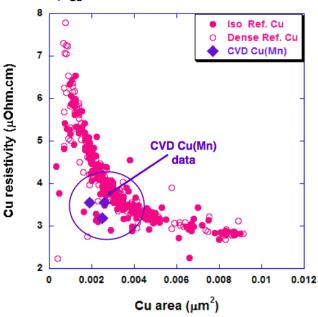

| Electrical Characterization of Narrow Trenches Filled with CVD of            |            |

| Cu-Mn Alloy                                                                  | 72         |

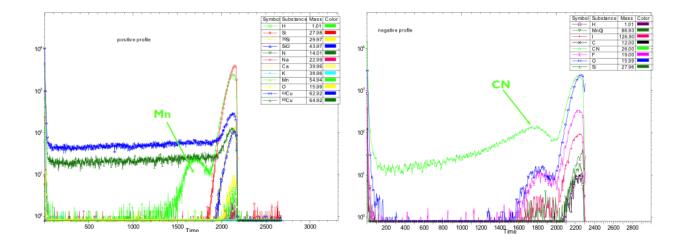

| Removal of Iodine from Copper Surface                                        | 74         |

| Metallization of Plastic Substrates                                          | 74         |

| 4.4 Conclusions | 75 |

|-----------------|----|

| References      | 77 |

| Chapter 5. Conformal Copper Seed Layers for Plating Through-Silicon Vias by Vapor |

|-----------------------------------------------------------------------------------|

| Deposition                                                                        |

| 5.1 Introduction                                                                  |

| 5.2 Experiments                                                                   |

| 5.3 Results and Discussion                                                        |

| Deposition of Barrier and Adhesion Layer                                          |

| Deposition of Seed Layer                                                          |

| Preliminary Electroplating Results                                                |

| 5.4 Conclusions                                                                   |

| References                                                                        |

| Chapter 6. Conclusions and Future Work |    |

|----------------------------------------|----|

| 6.1 Conclusions                        |    |

| 6.2 Future Work                        | 95 |

| References                             |    |

| Appendix I. CVD Reactor Operation Guide and Detailed Experimental Description of the C  | VD |

|-----------------------------------------------------------------------------------------|----|

| Processes                                                                               |    |

| Appendix II. List of Publications, Patent Applications, and Conference Presentations112 |    |

#### Acknowledgements

First and foremost, I would like to thank my advisor, Professor Roy G. Gordon, for his guidance and support that made this work possible. In addition to being a great teacher, his kindness and encouragement have made my graduate career more enjoyable and fulfilling than I had ever hoped. I am grateful for having had the opportunity to teach for him, to work with him on many exciting projects, and to share our passion for science, art, and music.

Besides my advisor, I would like to thank Professor Ted Betley, Professor Cynthia Friend, and Professor Joost Vlassak for serving on my committee. I thank my mentor and friend, Dr. Hoon Kim, for introducing me to the world of materials science and for giving me invaluable advices throughout my graduate studies. I was very fortunate to have worked with a group of very talented and friendly colleagues, and here I would like to express my warmest gratitude to all the former and current members of the Gordon Group.

I also need to extend my gratitude to the staffs at the Center for Nanoscale Systems (CNS) for their assistance during sample fabrication and characterization. I acknowledge our industrial collaborators: Dow Chemical for supplying the precursors, IBM, Applied Materials, and IMEC for providing some of the substrates and performing some of the analyses.

I thank Yu Lei and Xing Meng, my best friends in both college and graduate school, and Jing Yang for always being there for me when I needed them. They have made my graduate career a fruitful and joyful experience.

I thank Yue Liang, my girlfriend, for her love and inspiration. She is my most beautiful discovery at Harvard.

Finally, I thank my parents, to whom I dedicate this dissertation, for their continuous and unconditional love, and for giving me the wisdom and strength I need to succeed.

ix

To my parents

獻給 我的父親母親

#### **Chapter 1**

#### Introduction

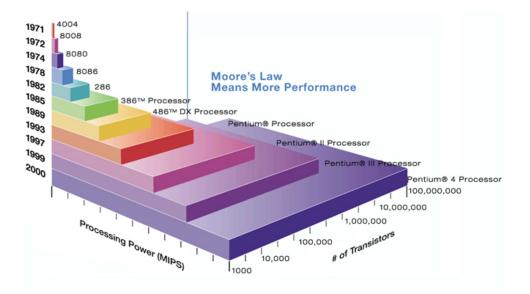

Gordon Moore, co-founder of Intel Corp., noted in his 1965 paper that the number of transistors in integrated circuits (IC) had doubled every year from the invention of the IC in 1958 until 1965 and predicted that the trend would continue for at least ten years.<sup>1</sup> His prediction was proven to be accurate and Moore's Law, which states that the number of transistors that can be placed inexpensively on an IC doubles approximately every two years, has been used to guide long-term planning and to set targets for research and development in the semiconductor industry for over 40 years. The periodic enhancements in IC density and performance gave rise to more powerful microelectronic devices with ever-increasing processing speed and memory capacity. Today, the impact of digital electronic devices has been witnessed on the global scale.

Figure 1.1 Moore's Law (Source: The Internet)

#### **1.1 Copper Interconnects in Microelectronics**

#### **Device Scaling and RC Delay**

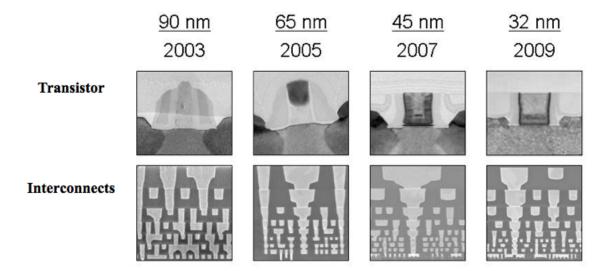

Continuous improvements in microelectronic devices have been achieved through evolutionary device scaling. On the transistor level, device density and performance improve as the gate length, gate dielectric thickness, and junction depth of the transistors are scaled. Each new technology generation generally represents a 0.7x reduction in feature size.<sup>2</sup> Intel's recent generation of microprocessors, fabricated by the 32 nanometer (32 nm) technology node manufacturing process, contain over one billion transistors while the average half-pitch (half the distance between identical transistors) was approximately 32 nm.

Figure 1.2 Cross-section of a transistor (top) and metal interconnects (bottom) in recent generations of processors (Source: Intel)

Transistors in microelectronics are formed in the front-end-of-line (FEOL) portion of IC fabrication. Metal wirings, also known as interconnects, are then deposited during the back-end-of-line (BEOL) portion to connect the individual transistors. Aluminum alloys were originally chosen for interconnect fabrication because of their low resistivity  $(3.0 - 5.0 \ \mu\Omega$ -cm) and

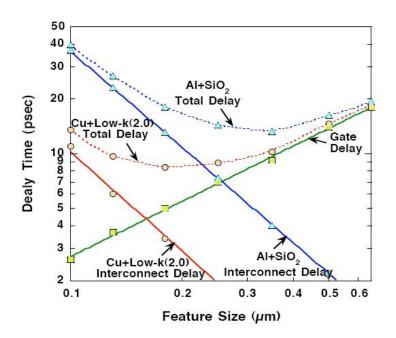

relatively low production costs. As the dimension of the devices scales to increase density and clock speed of the microprocessors, scaled interconnects suffer from increased resistance due to decreased conductor cross-sectional area and may also suffer from increased capacitance.<sup>3</sup> The interconnect delay (RC delay), which is proportional to the product of resistance and capacitance of the interconnect structure, degrades at a rate of 2x per technology generation assuming a constant metal aspect ratio and no change in conductor (i.e. Al) or dielectric materials (i.e. SiO<sub>2</sub>).<sup>2</sup> The RC delay is becoming dominant in determining the overall delay time, as shown in Figure 1.3. As a result, interconnect resistance and capacitance have become important parameters in determining IC design, packing density, and device performance. Interconnect delays must be minimized to build faster devices with lower power consumption.

Figure 1.3 Delay times versus feature size (Source: EE 311, Stanford University)

#### Low-k Dielectric Materials

Numerous low-*k* dielectric materials, from air (k = 1) to carbon doped oxide dielectrics ( $k \sim 3.8$ ), have been explored to replace silicon dioxide (SiO<sub>2</sub>, k = 3.9) to reduce the capacitance in

the interconnect systems.<sup>4</sup> Insertion of the low-*k* dielectric between the metal wires results in a significant reduction in RC delay. However, only a limited number of low-*k* materials have been introduced into production due to a significant number of integration and reliability issues, including thermally and mechanically induced cracking or adhesion loss, poor mechanical strength, moisture adsorption, low electrical breakdown, and poor thermal conductivity.<sup>5</sup> Dielectric materials with permittivity values less than ~ 2.5 are generally achieved by introducing porosity, which further increases moisture adsorption and reduces the mechanical strength of the materials.<sup>3</sup>

#### **Copper Interconnects**

To lower the resistance of the metal lines, copper (Cu) was first introduced in 1997 to replace aluminum alloy metallization due to its abundance, low resistivity (1.67  $\mu\Omega$ -cm, Table 1.1), and better reliability against electromigration (Table 1.2).<sup>6</sup> Highest performance is achieved when copper and low-*k* dielectrics are combined, as evidenced by the industry trend.

| Metal | Bulk Resistivity |  |

|-------|------------------|--|

|       | [μΩ-cm]          |  |

| Ag    | 1.63             |  |

| Cu    | 1.67             |  |

| Au    | 2.35             |  |

| Al    | 2.67             |  |

| W     | 5.65             |  |

Table 1.1 Resistivity of selected metals

Table 1.2 Comparison between Al and Cu

|                                             | Al            | Cu           |

|---------------------------------------------|---------------|--------------|

| Melting Point                               | 660 °C        | 1083 °C      |

| E <sub>a</sub> for Lattice Diffusion        | 1.4 eV        | 2.2 eV       |

| E <sub>a</sub> for Grain Boundary Diffusion | 0.4 - 0.8  eV | 0.7 – 1.2 eV |

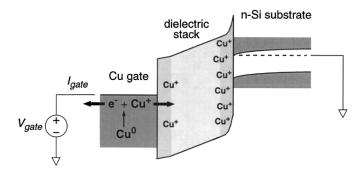

While copper metallization offers significant performance improvements, it also presents several integration and reliability challenges. One major concern is that copper atoms readily ionize and penetrate into most dielectric materials and then accumulate in the dielectric as Cu<sup>+</sup> space charge (Figure 1.4). Contamination to silicon devices leads to increased leakage in SiO<sub>2</sub>, increased junction leakage, and lower junction breakdown voltage.<sup>7</sup> As a result, copper must be encapsulated with diffusion barriers. In addition, the barrier layer must also provide adequate adhesion to both the dielectric material and the copper layers. High adhesive strength are required for copper interconnect microstructures to withstand the high residual stresses associated with thermal expansion mismatch and film growth processes, as well as the chemical mechanical planarization (CMP) process currently used in IC fabrication.<sup>8</sup>

Figure 1.4 Energy band diagram illustrating  $Cu^+$  penetration and accumulation under positive  $V_{gate}$  stress (Ref. 7)

#### **Diffusion Barriers**

Copper wires are encapsulated with diffusion barriers to prevent copper diffusion into silicon and dielectric materials under electric fields imposed during device operation (~  $1 \times 10^5$  V/cm).<sup>3</sup> The barrier materials are generally refractory metals or refractory metal nitrides.<sup>6</sup> Early studies used titanium (Ti), a highly reducing metal that binds strongly to oxygen, and titanium nitride (TiN) as barrier materials, but most companies in the industry have now settled on using

tantalum-based materials, such as tantalum metal (Ta) and tantalum nitride (TaN), as the diffusion barriers.<sup>9,10</sup> A list of various barriers for copper from previous studies and a comparison of tantalum- and titanium-based barriers are discussed in Reference 11.

Copper resistivity has been projected to increase dramatically with smaller feature size due to electron scattering from grain boundaries and conductor walls.<sup>12</sup> Although the resistivity of copper is greatly lower than that of aluminum alloys, the effective resistance of the copper line is determined by the actual cross-section of the line. As a result, diffusion barriers should be as thin as possible and those with high resistivity should be avoided. An ideal diffusion barrier must be free of defects, smooth, continuous, and conformal at minimal thickness. The barrier should also provide good adhesion strength and show no interaction with dielectric insulators and the copper seed layer. A dense, amorphous barrier is usually preferred to avoid fast diffusion path for copper, such as grain boundaries.<sup>6</sup>

#### Seed Layers

Copper interconnects are built by electroplating copper in the open trenches in the patterned insulator layer.<sup>13</sup> Electroplating is typically carried out in a bath that contains copper sulfate (CuSO<sub>4</sub>) electrolytes and other additives (accelerators, suppressors, etc.) to achieve consistent fill and to improve film quality. The electroplating method allows low process temperature, high deposition rates, and complete via- and trench-filling capabilities. Most plating techniques require a thin seed layer as an electrode. These seed layers must have low resistivity, conformal step coverage, smooth surface morphology, and strong adhesion to the underlying barrier layer. If the seed coverage is discontinuous, then feature fill during copper electroplating becomes difficult and voids will typically be observed along the feature sidewalls.<sup>6</sup>

#### **The Damascene Process**

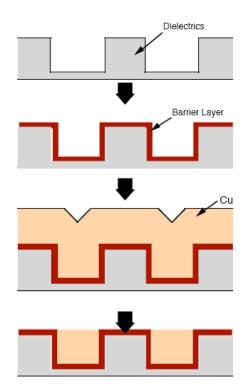

Figure 1.5 A typical damascene process (Source: The Internet)

The damascene process<sup>13</sup> is adopted by the semiconductor industry to fabricate copper interconnects. The most common process integration steps to form copper interconnects are: (1) deposit the damascene or dual damascene interlevel or intermetal dielectric materials, (2) pattern and etch the damascene or dual damascene structure into the dielectrics, (3) deposit a barrier/seed stack and fill the openings with electrodeposited copper, (4) anneal the wafers to stabilize the microstructure, (5) polish the excess copper and barrier away using CMP (Figure 1.5). Steps 1 through 5 are repeated for multi-layered interconnects. The final copper layer is then passivated and prepared for packaging and assembly.

#### **Electromigration Reliability**

Electromigration is a reliability problem in which metal atoms move in the direction of the current flow due to momentum transfer. J. R. Black developed an empirical model in the 1960's to estimate the mean time to failure (*MTTF*) of a metal wire, taking electromigration into consideration:

$$MTTF = AJ^{-n}e^{\frac{\Delta H}{kT}}$$

(1.1)

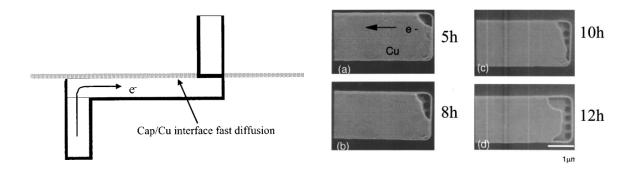

where *A* is a constant based on the cross-sectional area of the interconnect, *J* is the current density,  $\Delta H$  is the electromigration activation energy, *k* is the Boltzmann's constant, *T* is the temperature, and *n* a scaling factor.<sup>14</sup> It is clear that electromigration is becoming a major concern due to the aggressive scaling of interconnect dimensions and the ever-increasing current densities at operation. Compared to aluminum interconnects, copper interconnects are more robust against electromigration failure due to stronger Cu-Cu bond and higher melting temperature relative to that of aluminum.<sup>15</sup> The mass transport mechanism of copper electromigration, unlike that of aluminum electromigration, is almost exclusively interfacial or surface diffusion. As a result, copper electromigration is more a function of the nature of the interfaces available for mass transport.<sup>16</sup> In today's copper damascene processes, copper wires are typically protected by a liner to prevent diffusion through the intralevel dielectric. Unfortunately, the CMP process does not allow protection of the top copper surface by a liner. Therefore, the chemical-mechanical polished surface, which is usually covered with a dielectric capping layer, is the fast diffusion path.<sup>16</sup>

Figure 1.6 Schematic of a Cu interconnect showing the Cu/capping layer interface is the fast diffusion path in an electromigration test (left), SEM showing copper electromigration during the test (right) (Ref. 16)

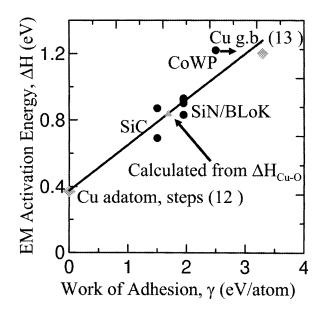

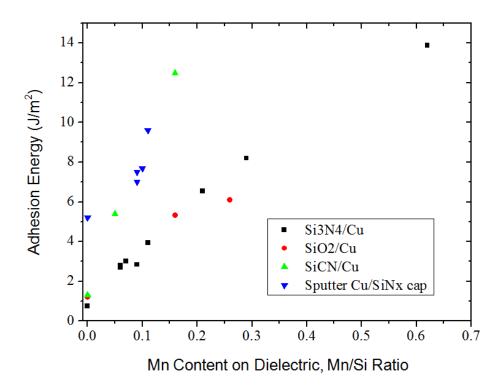

Lane *et al.* demonstrated that the adhesion strength at the Cu/capping layer interface is directly correlated to the electromigration lifetime of copper conductors (Figure 1.7).<sup>16</sup> As a result, capping and liner materials must be carefully chosen and adhesion at Cu/capping layer interface must be improved to achieve better electromigration reliability and longer lifetime.

Figure 1.7 Electromigration activation energy as a function of the work of adhesion at Cu/capping layer interfaces

(Ref. 16)

#### **1.2 Deposition Techniques**

Microfabrication is a highly complex collection of technologies that is used to make microelectronic devices. Over 1000 steps, in which the first 500 steps belong to the FEOL portion and the next 500 steps belong to the BEOL portion, are involved in building today's microprocessors. Thin film deposition is the most ubiquitous and critical of the processes used to manufacture microelectronic devices, and the deposition techniques typically fall into two broad categories: physical vapor deposition and chemical vapor deposition.

#### **Physical Vapor Deposition (PVD)**

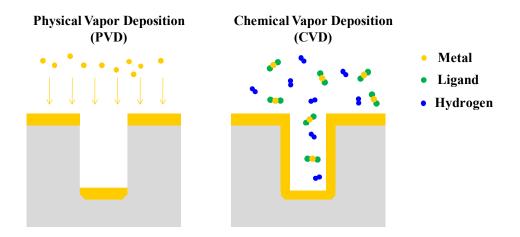

The two physically based methods for depositing thin films are evaporation and sputtering. They are called physical vapor deposition processes because these techniques do not involve chemical reactions. The vapors of the material to be deposited are produced either by heating or by energetic ion bombardment.

The metal layers for all of the early generations of semiconductor technologies were deposited by evaporation. In an evaporator, the wafers are loaded into a high-vacuum chamber that is commonly pumped with a cryopump. The material to be deposited is loaded into a crucible and is heated by an embedded resistance heater and an external power supply. Since the pressure inside the chamber is very low ( $< 10^{-5}$  Torr), vapors of the material travel across the chamber in a straight line until they strike the substrate surface, where they accumulate and form a film.<sup>17</sup> A mechanical shutter is typically used in front of the container to start and stop the deposition abruptly. There are two basic types of crucible heating systems: resistive heating and electron-beam heating.

Sputtering has the ability to achieve better step coverage and to produce well-controlled layers of compound materials and alloys than evaporation techniques. In a sputtering system, the plasma chamber is arranged so that high-energy ions strike the target that contains the material to be deposited. Because of the higher pressure ( $\sim 10^{-3}$  Torr) in sputtering systems, the atoms experience more gas-phase collisions and produce films with higher conformality. Due to the physical nature of the process, sputtering can be used to deposit a wide variety of materials. DC sputtering is usually favored while depositing elemental metals due to its high sputter rates. RF plasma is used to deposit insulting materials such as SiO<sub>2</sub>.<sup>17</sup> Sputtering is now the primary technique used to deposit diffusion barrier (TaN, TiN), adhesion layer (Ta, Ti), and seed layer (Cu) in copper interconnect systems.

Figure 1.8 Schematic diagrams of physical vapor deposition and chemical vapor deposition

#### **Chemical Vapor Deposition (CVD)**

Although most metal films for silicon ICs are deposited using physical vapor deposition methods, they have major problems associated with step coverage. This is a particular concern with future technologies where very small, high aspect ratio features require conformal step coverage. Chemical vapor deposition has the best ability to achieve conformal step coverage and produces the least substrate damage.<sup>17</sup>

Chemical vapor deposition is the process of chemically reacting a volatile compound of a material to be deposited, with other gases, to produce a nonvolatile solid that deposits atomistically on a substrate. CVD methods have been used to produce a variety of films and coatings of metals, semiconductors, and insulators with desirable electrical, optical, and mechanical properties.<sup>18</sup> CVD processes are often chosen over other vacuum deposition techniques for their affordable equipment cost and operating expenses, suitability for both batch and semi-continuous operation, and compatibility with other processing steps. Other advantages of CVD processes include the ability to achieve surface-selective deposition and to coat or superfill high aspect ratio 3-dimensional structures. These features will be highlighted in the following chapters. Many variants of CVD processing, including atmospheric pressure (APCVD), lowpressure (LPCVD), and plasma-enhanced (PECVD), have been researched and developed. Metalorganic CVD (MOCVD) is now widely used to grow epitaxial compound semiconductor, dielectrics insulators, and metal films. While other CVD process variants are differentiated physically on the basis of pressure or use of plasmas, MOCVD is distinguished by the chemical nature of the precursor gases. One advantage of metalorganics is their generally high volatility at moderately low temperatures. Carbon contamination of film, however, is a major disadvantage.<sup>18</sup>

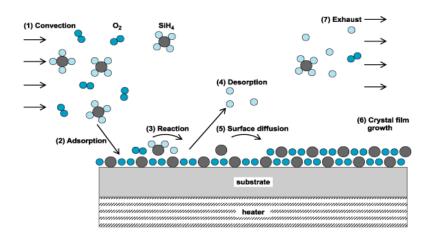

The fundamental sequential steps that occur in a typical CVD process include: (1) convective and diffusive transport of reactants from the gas inlets to the reaction zone, (2) transport of the initial reactants and their products to the substrate surface, (3) adsorption (chemical and physical) and diffusion of these species on the substrate surface, (4) heterogeneous reactions catalyzed by the surface leading to film formation, (5) desorption of the volatile by-

products of surface reactions, and (6) convective and diffusive transport of the reaction byproducts away from the reaction zone.

Figure 1.9 Sequence of transport and reaction processes during CVD SiO<sub>2</sub> film growth

(Source: The Internet)

#### **First Order Model of Deposition**

A first order model of is presented here to better understand the process of chemical vapor deposition.<sup>17</sup>

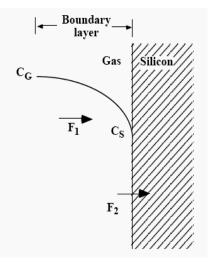

Figure 1.10 Mass transfer of reactants ( $F_1$ ) and surface reaction ( $F_2$ ) during a CVD process

(Source: ES 174, Harvard University)

Mass transfer of reactants through the boundary layer is one of the two most important steps that determine the overall growth rate.  $F_1$  denotes the flux of the mass transfer of reactants and can be described as:

$$F_1 = h_G (C_G - C_S)$$

(1.2)

where  $h_G$  is the mass transfer coefficient,  $C_G$  is the concentration of the reactant in main gas flow, and  $C_S$  is the concentration of the reactant at wafer surface. The other important step in determining the growth rate is the surface reaction step. The flux,  $F_2$ , can be described as:

$$F_2 = k_s C_s \tag{1.3}$$

where  $k_S$  is the chemical surface reaction rate. At steady-state, the two processes act in series and must be equal to each other,  $F_1 = F_2$ , so:

$$C_s = C_G \left(\frac{h_G}{k_s + h_G}\right) \tag{1.4}$$

The film deposition rate is given by:

$$v = \frac{F}{N} = \frac{k_s h_G}{k_s + h_G} \frac{C_G}{N}$$

(1.5)

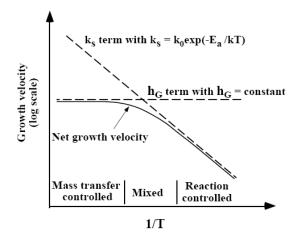

where *N* is the number of atoms per unit volume incorporated into the film. From Equation 1.5, it is clear that the deposition rate is determined by the smaller of  $k_S$  or  $h_G$ , therefore leading to two limiting cases:

1. If  $k_s \ll h_G$ , then:

$$v \approx k_s \frac{C_G}{N} \tag{1.6}$$

This is called the surface reaction-controlled regime. When deposition occurs in this regime (usually at lower temperatures), the deposition process is very sensitive to temperature as the surface reaction rate constant obeys the Arrhenius equation:

$$k_s = k_0 e^{-E_a/kT} \tag{1.7}$$

2. If  $k_s >> h_G$ , then:

$$v \approx h_G \frac{C_G}{N} \tag{1.8}$$

This is called the mass transfer-controlled regime. When deposition occurs in this regime (usually at higher temperatures), the deposition rates depend primarily on mass transfer, or the gas phase diffusion, of the reactants and are relatively insensitive to temperature.  $C_s$  in this case approaches zero because the reactants are used up at the surface as soon as they arrive. Figure 1.11 summarizes the temperature dependence of the deposition rates of CVD processes.

Figure 1.11 Temperature dependence of CVD growth velocities (Source: ES 174, Harvard University)

#### **1.3 Characterization of Thin Films**

Characterization techniques are crucial to the development of thin film science and technology. Information about various structural and chemical properties can be evaluated by modern analytical techniques with high levels of precision and accuracy. A list of modern techniques employed in the characterization of thin film materials in this thesis is shown in Table 1.3.

| Primary beam | Energy range  | Secondary<br>signal | Technique                                       | Application                  |

|--------------|---------------|---------------------|-------------------------------------------------|------------------------------|

| Electron     | 0.3 – 30 keV  | Electron            | Scanning electron<br>microscopy (SEM)           | Surface morphology           |

|              | 100 – 400 keV | Electron            | Transmission electron<br>microscopy (TEM)       | High-resolution structure    |

|              | 1 – 30 keV    | X-ray               | Energy-dispersive X-ray<br>spectroscopy (EDX)   | Surface region composition   |

|              | 100 – 400 keV | Electron            | Electron energy loss<br>spectroscopy (EELS)     | Local small-area composition |

| Ion          | 1 – 15 keV    | Ion                 | Secondary ion mass<br>spectrometry (SIMS)       | Trace composition vs. depth  |

|              | > 1 MeV       | Ion                 | Rutherford backscattering<br>spectrometry (RBS) | Composition vs. depth        |

| Photon       | > 1 keV       | Electron            | X-ray photoelectron<br>spectroscopy (XPS)       | Surface composition          |

|              | > 1 keV       | X-ray               | X-ray fluorescence (XRF)                        | Composition                  |

|              | > 1 keV       | X-ray               | X-ray diffraction (XRD)                         | Crystal structure            |

Table 1.3 Analytical techniques employed in thin film science and technology (Ref. 18)

#### **Thickness and Structural Characterization**

Thickness, refractive index, and other optical properties of dielectric thin films are typically measured by ellipsometry. Ellipsometry is an optical technique that measures the change of polarization state of a linearly polarized light beam upon reflection or transmission at the surface of a film. Surface morphology of the thin films can be evaluated using an atomic force microscope (AFM). AFM consists of a microscale cantilever with a sharp tip that is used to scan the specimen surface. When the tip is brought into proximity of a sample surface, forces between the tip and the sample lead to a deflection of the cantilever according to Hooke's law, the deflection is then measured using a laser spot reflected from the top surface of the cantilever.

Scanning electron microscope (SEM) is used to analyze surface morphology and step coverage of the thin films in high aspect ratio (AR) features. SEM is a powerful, perhaps the most widely employed, imaging tool with high resolution (~ 10 nm) and element-dependent contrast. Sample preparation for top-view and cross-section analyses is straightforward. SEM detects the intensity of the backscattered electrons or secondary electrons produced from interaction of the high-energy electron beam with the atoms at or near the surface of the sample, producing images that contain information about the sample's surface topography, composition, and electrical conductivity.

Transmission electron microscope (TEM) transmits a high-energy focused beam of electrons through an ultra-thin specimen that is transparent to electrons. An image is formed from the interaction of the electrons transmitted through the specimen and is magnified and focused onto an imaging device. The resolution of the TEM is about an order of magnitude better than that of the SEM. TEM is used to obtain structural information of specimens. Crosssectional TEM samples can be prepared by two different methods. The first method sandwiches two pieces of the same sample together and the center of the sample is thinned down to a few hundred microns using a mechanical polishing method. The thinned sample is then ion-milled to a desired thickness of 10 - 50 nm. The second method is a lift-out method using a focused ion beam (FIB). The area of interest is first covered by a protective coating (typically platinum, tungsten, or carbon). A wedge is then milled by the FIB and the lamella is lifted out from its hole using an AutoProbe<sup>®</sup>. Next, the wedge is welded to the top of the TEM grid post by depositing

platinum or tungsten. The wedge is thinned to about 1.5 micron with a current < 300 pA and to the desired thickness using a lower current (20 – 40 pA).

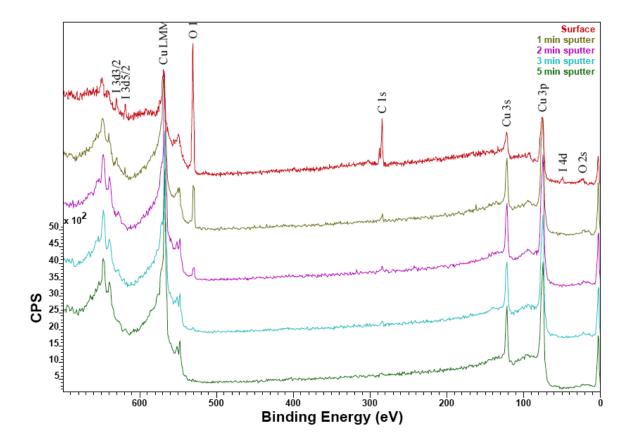

#### **Chemical Characterization**

Energy-dispersive X-ray spectroscopy (EDX), X-ray photoelectron spectroscopy (XPS), Rutherford backscattering spectroscopy (RBS), and secondary ion mass spectrometry (SIMS) are useful techniques for elemental analysis or chemical characterization of the thin film samples.

EDX uses a high-energy incident beam to excite and eject an electron in an inner shell of the atoms in a sample, which creates a hole that is then filled by an electron from an outer shell. The difference in energy between the energy shells is released in the form of an X-ray, which is characteristic of the material, and is measured by an energy-dispersive spectrometer.

XPS measures the elemental composition, empirical formula, chemical state, and electronic state of the elements within a material. The sample is analyzed by irradiating of a beam of X-ray while simultaneously measuring the kinetic energy and number of electrons that escape from the top 1 - 10 nm of the material being analyzed. Because the energy of a particular X-ray wavelength ( $E_{photon}$ ) is known, the electron binding energy ( $E_{binding}$ ) of each of the emitted electrons can be determined by:

$$E_{binding} = E_{photon} - (E_{kinetic} + \phi)$$

(1.9)

where  $E_{kinetic}$  is the kinetic energy of the electron measured by the instrument, and  $\phi$  is the work function of the spectrometer.

RBS is used to determine the structure and composition of materials by measuring the backscattering of a beam of high-energy ions impinging on a sample. Rutherford backscattering

can be described as an elastic collision between a high kinetic energy particle from the incident beam (the projectile) and a stationary particle located in the sample (the target). Considering the conservation of momentum and kinetic energy, the energy of the scattered projectile ( $E_1$ ) is reduced from the initial energy ( $E_0$ ):

$$E_1 = kE_0 \tag{1.10}$$

where *k* is the kinematical factor:

$$k = \left(\frac{m_1 \cos \theta_1 \pm \sqrt{m_2^2 - m_1^2 (\sin \theta_1)^2}}{m_1 + m_2}\right)^2$$

(1.11)

where  $m_1$  is the mass of the projectile,  $m_2$  is the mass of the target nucleus, and  $\theta_1$  is the scattering angle of the projectile.

SIMS is the most sensitive surface analysis technique and is used to analyze the composition of thin films by simultaneously sputtering the surface of the sample with a focused primary ion beam and collecting and analyzing the ejected secondary ions that are then measured with a mass spectrometer.

#### **Adhesion Test**

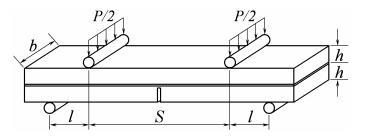

The adhesion (debonding) energy in multi-layer thin film structures is quantitatively measured by a fracture mechanics technique called the four-point bend test. A schematic illustration of a four-point bend test sample is shown in Figure 1.12.

Figure 1.12 Schematic illustration of a four-point bend sample (Ref. 19)

Adhesion samples are prepared by cleaving the Si-based substrates into 12 mm x 60 mm strips. These strips are then bonded face-to-face using epoxy. Notches are made in the samples using a diamond saw. The sample is loaded at a constant displacement rate until interfacial cracks are achieved. If P is the load at which the crack propagates along the interface, then to corresponding adhesion energy (G) is: <sup>19</sup>

$$G = \frac{21P^2l^2(1-v^2)}{16Eb^2h^3}$$

(1.12)

where E and v are the elastic modulus and Poisson's ratio of the Si substrate, l is the distance between the inner and outer loading pins, b is the width of the specimen, and h is the wafer thickness. The four-point bend test is now used as a standard method in the semiconductor industry for determining interfacial adhesion energy.

More detailed discussions on thin film deposition techniques, film growth mechanisms, and characterization methods can be found in References 18 and 20.

#### References

- <sup>1</sup> G. Moore, *Electronics*, **38**, 114 (1965).

- <sup>2</sup> M. Bohr, Int. El. Devices Meet., 241 (1995).

<sup>3</sup> R. Havemann and J. Hutchby, *Proc. IEEE*, **89**, 586 (2001).

- <sup>4</sup> A. Grill, J. Appl. Phys., **93**, 1785 (2003).

- <sup>5</sup> A. Grill, C. Jahnes, J. Ott, V. Patel, J. Hummel, R. Mih, and J. Liu, *Proc. Electrochem. Soc.*, **98**, 118 (1998).

<sup>6</sup> S. Merchant, S. Kang, M. Sanganeria, B. van Schravendijk, and T. Mountsier, *JOM*, **6**, 43 (2001).

<sup>7</sup> A. Loke, J. Wetzel, P. Townsend, T. Tanabe, R. Vrtis, M. Zussman, D. Kumar, C. Ryu, and S. Wong, *IEEE Trans. Electron Devices*, **46**, 2178 (1999).

<sup>8</sup> M. Lane, R. Dauskardt, N. Krishna, and I. Hashim, J. Mater. Res., 15, 203 (2000).

- <sup>9</sup> K. Park, K. Kim, I. Raaijmakers, and K. Ngan, J. Appl. Phys., 80, 5674 (1996).

- <sup>10</sup> T. Oku, E. Kawakami, M. Uekubo, K. Takahiro, S. Yamaguchi, M. Murakami, *Appl. Surf. Sci.*, 99, 265 (1996).

- <sup>11</sup> C. Ryu, H. Lee, K. Kwon, A. Loke, and S. Wong, *Solid State Technology*, **42**, 53 (1999).

- <sup>12</sup> The International Technology Roadmap for Semiconductors, http://public.itrs.net (2009).

- <sup>13</sup> P. Andricacos, C. Uzoh, J. Dukovic, J. Horkans, and H. Deligianni, *IBM J. Res. Develop.*, 42, 567 (1998).

- <sup>14</sup> J. Black, *IEEE Trans. On Electron Devices*, **16**, 338 (1969).

- <sup>15</sup> C. Hau-Riege, *Microelectronics Reliability*, 44, 195 (2004).

- <sup>16</sup> M. Lane, E. Liniger, and J. Lloyd, J. Appl. Phys., 93, 1417 (2003).

- <sup>17</sup> S. Campbell, *The Science and Engineering of Microelectronic Fabrication*, Second ed.

(Oxford University Press, New York, 2001).

- <sup>18</sup> M. Ohring, *Materials Science of Thin Films*, Second ed. (Academic Press, San Diego, 2002).

- <sup>19</sup> R. Dauskardt, M. Lane, Q. Ma, and N. Krishna, *Engineering Fracture Mechanics*, **61**, 141 (1998).

<sup>20</sup> D. Smith, *Thin Film Deposition: Principles and Practice*, (McGraw-Hill Inc., New York, 1995).

#### Chapter 2

# Chemical Vapor Deposition (CVD) of Manganese Silicate (MnSi<sub>x</sub>O<sub>y</sub>) Diffusion Barrier

#### **2.1 Introduction**

Copper (Cu) is now becoming the standard material for connecting transistors in microelectronic devices. However, transistors cannot function properly if copper diffuses into them. Diffused copper may also reduce the resistance of the insulating material between the metal wires. For these reasons, copper must be confined inside diffusion barriers. In addition, barriers to oxygen and water are desired to separate copper from oxidants in the environment and to prevent oxidation. Sputtered tantalum nitride (TaN) diffusion barriers are currently used in the semiconductor industry. Although TaN is an effective diffusion barrier, copper does not adhere strongly to TaN. As a result, tantalum (Ta) metal, which adheres much stronger to copper metal, is sputtered on top of the TaN barrier as an adhesion layer to enhance the durability of interconnect structures. Following Ta deposition, a thin copper seed layer is sputtered and the trenches and holes are filled with electroplated copper.

As the dimensions of microelectronic circuits are being reduced, the non-conformal nature of sputtered barrier (TaN), adhesion (Ta) and seed (Cu) layers has caused problems. These layers tend to be thicker near the top openings, so that the remaining openings are narrower at the top than the bottom of the features. Electroplating copper in these features can cause formation of voids, which can later lead to failure of the interconnections. Another challenge arises from the roughness on the sidewalls of the features, which may prevent deposition on recessed regions

that are shielded from the line of sight to the sputtering target. If the barrier layer is missing in these areas, copper may diffuse out through these holes contaminate the underlying layers. If the adhesion layer is missing, the reliability of the interconnect system may be affected due to reduced adhesion between copper and the barrier. If the seed layer is missing, copper electroplating will not take place on the oxidized surface of the exposed underlying layer, producing voids in the copper. Therefore, there is a need for methods that can produce highly conformal diffusion barriers, adhesion layers, and seed layers in the interconnect system. CVD and atomic layer deposition (ALD) are methods that can potentially achieve such high conformality.<sup>1</sup>

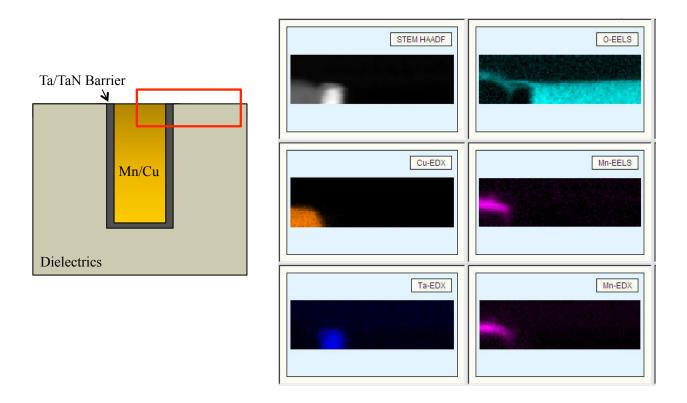

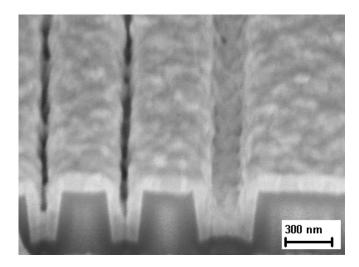

One other problem with current technology is that both TaN and Ta have much higher resistivity values than copper. Thus by displacing copper metal, these layers increase the overall resistance of interconnects. The RC delay time increases with the resistance of the system, and therefore the volume of barrier material should be minimized in order to form the fastest circuits. Ideally, a barrier should not occupy any of the volume reserved for copper. Such a "zero-thickness barrier" can be realized by sputtering a manganese-copper alloy, from which manganese diffuses into the surface of silica insulator at 450 °C.<sup>2,3</sup> The resulting self-aligned barrier layer of amorphous manganese silicate (MnSi<sub>x</sub>O<sub>y</sub>), just a few nanometers thick, remains part of the insulator surface, whose dimensions are not significantly changed by in-diffusion of the manganese. The resulting interconnects have lower resistance than ones made with conventional TaN barriers, and have proven to be even more durable.<sup>4,5</sup>

The self-aligned MnSi<sub>x</sub>O<sub>y</sub> barriers are formed by sputtering Mn-Cu alloy, therefore, they are still subject to the conformality problems of sputtered barriers. Voids in electroplated copper may form under overhangs near the tops of features or inside rough areas on the sidewalls. In this

chapter, a new way to make conformal self-aligned  $MnSi_xO_y$  barriers using CVD of manganese metal is proposed. Vapors of a manganese compound react with silica surfaces to form a thin amorphous layer of manganese silicate mainly within the surface of the silica. The  $MnSi_xO_y$ layer is found to be an excellent barrier against diffusion of copper,  $O_2$  and  $H_2O$ . CVD Mn also greatly increases the adhesion of copper to capping layers of SiCNOH. The layer is completely conformal inside the surfaces of holes and trenches.

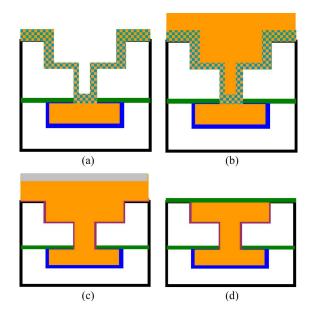

Figure 2.1 Schematics of the fabrication process for Cu dual-damascene interconnects with self-formed MnSi<sub>x</sub>O<sub>y</sub>

barrier layer. (a) Deposition of CuMn seed layer by sputtering, (b) Cu deposition by electroplating, (c) Annealing for MnSi<sub>x</sub>O<sub>y</sub> layer, (d) Removal of excess Cu and Mn by CMP and deposition of dielectric capping layer (Ref. 4)

#### **2.2 Experiments**

#### **Metal Amidinate Precursors**

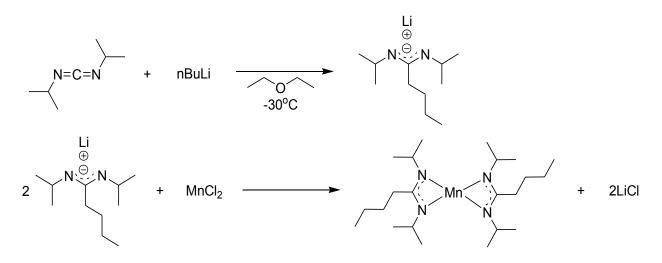

The compound that serves as a precursor for manganese is called bis(N,N'-diisopropylpropionamidinato) manganese(II). The compound was synthesized by methods

similar to those described in Reference 6 (Figure 2.2). It is a pale yellow crystalline solid that melts at about 60 °C to a clear liquid.

Figure 2.2 Synthesis of manganese (II) amidinate

CVD and ALD precursors need to be highly reactive toward the surfaces of substrates and also to the surface prepared by a complementary precursor such as H<sub>2</sub>O, NH<sub>3</sub>, or H<sub>2</sub>. These compounds must also be volatile and thermally stable at growth temperatures, and preferably the reaction byproducts should be nonreactive and noncorrosive. CVD precursor chemistry has been dominated by halides, alkoxides,  $\beta$ -diketonates, alkyls, and cyclopentadienyl derivatives.<sup>6</sup> Alkylamide precursors have attracted more attention in recent years because these compounds do not have M-C bonds, resulting in minimal carbon incorporation in the deposited films, and the low M-N bond strengths as compared to the M-Cl and M-O bonds allowed deposition at relatively low temperatures.<sup>7</sup> These amide derivatives produce no corrosive byproducts, unlike metal halides. Metal amidinates are alternatives to alkylamides. The amidinate ligand can be tuned by substitution of the alkyl groups to be bulky enough to limit oligomerization and therefore increase the volatility of metal amidinate compounds. The bidentate chelating effect, on the other hand, should increase the thermal stability of resulting metal compounds.<sup>6</sup>

#### **CVD Reactor Setup and Characterization Methods**

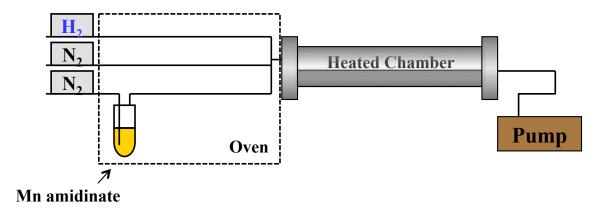

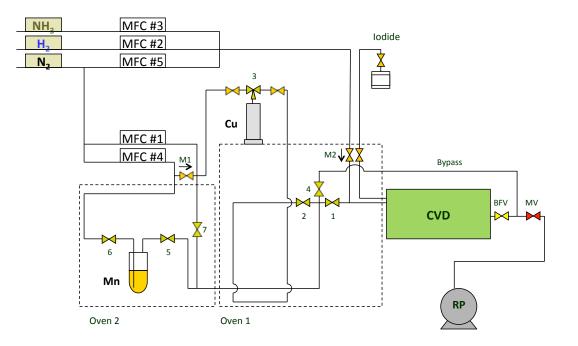

For the CVD experiments, the manganese precursor was evaporated from the liquid in a bubbler at a temperature of 90 °C into a 60 sccm flow of highly purified nitrogen (concentrations of water and oxygen less than  $10^{-9}$  of the N<sub>2</sub>). The manganese precursor would react immediately with oxygen or water to form a black material when it is exposed to air. The vapor pressure of the precursor is estimated to be around 0.1 mbar at 90 °C.

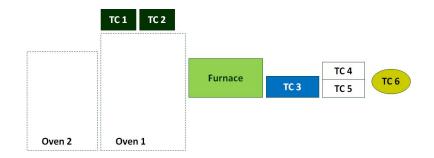

Figure 2.3 Schematic diagram of the CVD system

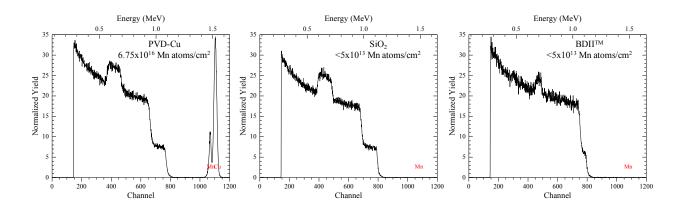

The substrates of silica were either thermally oxidized silicon or silica deposited by ALD. The CVD process was carried out in a hot-wall tube reactor (diameter 36 mm) within a tube furnace at temperatures between 200 and 400 °C and a total pressure of about 5 Torr. The amount of manganese deposited was measured by Rutherford backscattering spectroscopy (RBS). The MnSi<sub>x</sub>O<sub>y</sub> formation was evaluated by cross-sectional high-resolution transmission electron microscopy (HRTEM). The effectiveness of the MnSi<sub>x</sub>O<sub>y</sub> as a barrier to diffusion of copper was tested in four ways: (1) optical appearance, (2) sheet resistance, (3) copper silicide formation, and (4) capacitance-voltage (CV) analysis of capacitors. For copper diffusion tests, 8 nm of SiO<sub>2</sub> were grown on HF-etched silicon wafers by ALD at 250 °C, followed by CVD Mn at 350 °C for 10 min, which formed 2.3 nm of manganese metal. Control samples of SiO<sub>2</sub> omitted the CVD Mn treatment. Then copper layers with thicknesses around 200 nm were deposited on top of the CVD MnSi<sub>x</sub>O<sub>y</sub> or SiO<sub>2</sub> layers. Post-deposition annealing treatments were carried out at temperatures of 400, 450, and 500 °C for one hour in a pure nitrogen atmosphere. For CV analysis, CVD Mn layer is deposited on 300 nm thermal SiO<sub>2</sub> on Si. Copper pads (500  $\mu$ m diameter circle) were thermally evaporated using a shadow mask. CV characteristics of the metal-oxide-semiconductor (MOS) structure were measured with a HP 4275A meter in a shielded probe station at room temperature. The copper pad samples were used for Bias-Temperature Stress (BTS) test that was conducted at 250 °C under 1 MV/cm bias condition in Ar ambient. CV was then measured at room temperature after the stress treatment.

#### **2.3 Results and Discussion**

#### Formation of Manganese Silicate (MnSi<sub>x</sub>O<sub>y</sub>)

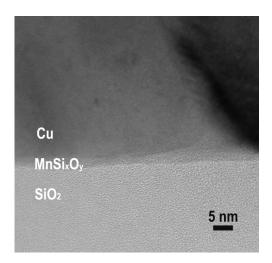

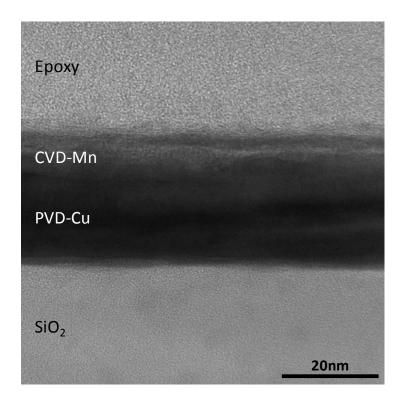

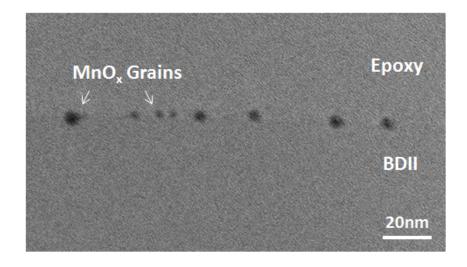

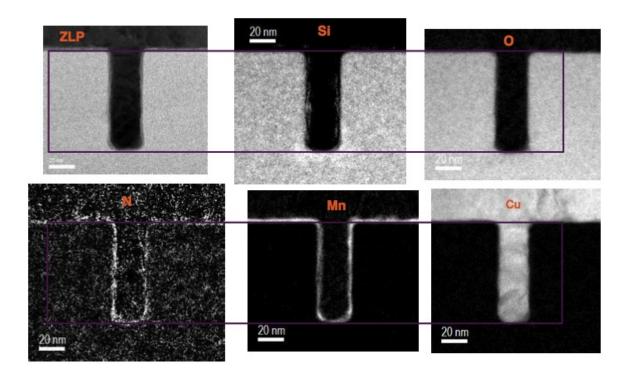

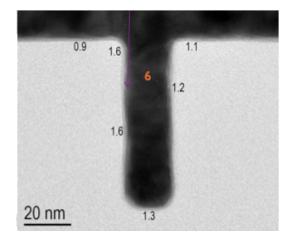

Thin manganese layers (2.3 nm) deposited on SiO<sub>2</sub> did not contribute to any conductivity by 4-point probe (>  $10^6$  ohm/square). Since manganese metal may be oxidized when the sample was taken out into the air for measurement, it is not clear from this measurement whether the CVD process had deposited manganese metal or some insulating manganese compound. To confirm manganese metal deposition, CVD was carried out on 50 nm of Cu film that had been evaporated onto SiO<sub>2</sub>/Si substrates. The resulting structure was examined by cross-sectional HRTEM. Figure 2.4 shows that the manganese metal had diffused through the thin copper layer and reacted with the SiO<sub>2</sub> to form an amorphous manganese silicate (MnSi<sub>x</sub>O<sub>y</sub>) layer, with thickness about 2 – 5 nm, between copper and SiO<sub>2</sub>. The MnSi<sub>x</sub>O<sub>y</sub> layer is thicker near grain boundaries in the copper, along which manganese diffusion is faster. This result is an evidence of manganese metal deposition.

Figure 2.4 Cross-sectional HRTEM of CVD Mn on PVD Cu/SiO<sub>2</sub>

#### **Copper Diffusion Barrier Tests**

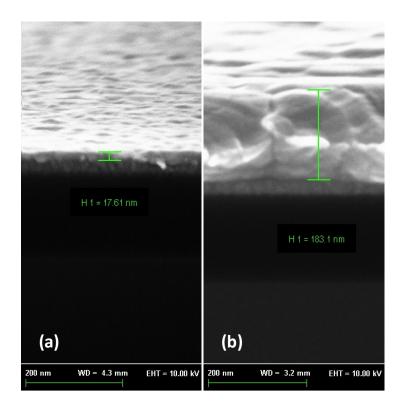

The effectiveness of  $MnSi_xO_y$  as a copper diffusion barrier was evaluated using a sample structure PVD Cu (200 nm)/CVD Mn (2.3 nm)/ALD SiO<sub>2</sub> (8 nm)/Si. A MnSi<sub>x</sub>O<sub>y</sub> layer was formed between the copper and ALD SiO<sub>2</sub> layers. The shiny copper color and sheet resistances of these samples were unchanged by anneals in nitrogen at 400 or 450 °C. After a 500 °C anneal, the control sample, which did not have any  $MnSi_xO_y$  layer, turned black and its sheet resistance increased by a factor of 200 as a result of massive copper diffusion through the thin ALD SiO<sub>2</sub> into the silicon. The sample treated with CVD of manganese, by contrast, retained its shiny copper color and increased its resistance only slightly.

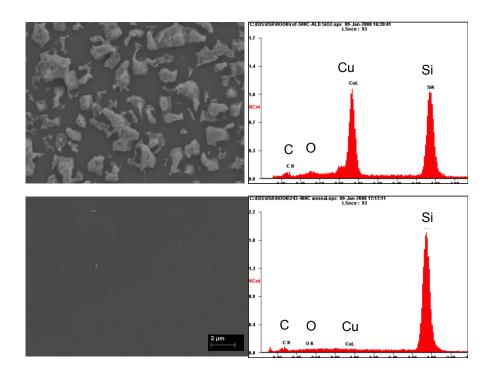

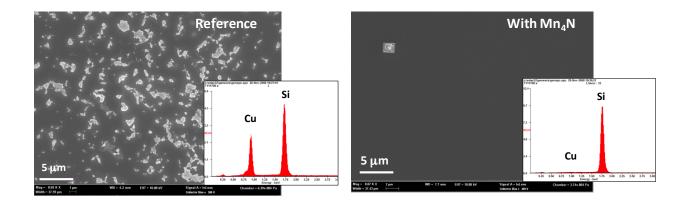

To further analyze the diffusion of copper, the remaining copper layers were dissolved in nitric acid and the manganese silicate and silica layers were removed by dilute HF. The etched surfaces were then analyzed by an energy-dispersive X-ray spectrometer (EDX) and scanning

electron microscope (SEM). Figure 2.5 shows the SEM results after a 500 °C anneal for 1 hour. The few Cu-containing spots appeared to be copper silicide crystallites oriented by the crystal directions of the silicon. The surface of the control sample was covered by copper silicide. The control sample showed a large Cu signal in EDX analysis that was even stronger than the silicon signal, indicating that the thin ALD SiO<sub>2</sub> allowed copper diffusion. The CVD Mn-treated samples did not show copper by large-area EDX. A few small areas of the SEM image did show some copper by EDX, indicating some localized breakdown of the MnSi<sub>x</sub>O<sub>y</sub> barrier at 500 °C. These spots might arise from dust or other defects in the films, which were not processed in a clean-room environment.

Figure 2.5 SEM and EDX of etched Si surface after annealing at 500  $^{\circ}C$  (a) with SiO\_2 alone, and (b) with CVD  $MnSi_xO_y \text{ on }SiO_2$

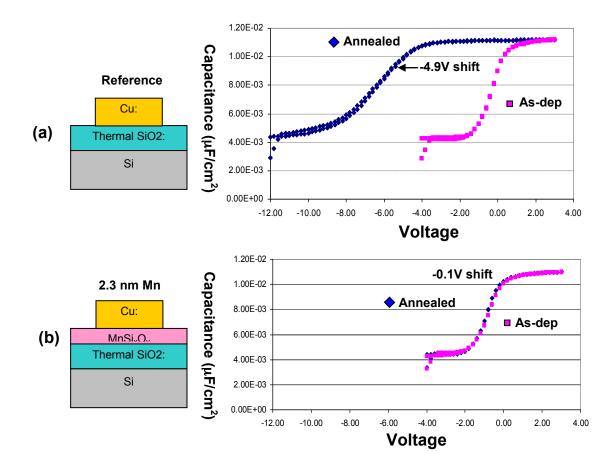

An electrical test of barrier properties was carried out by patterning the Cu into capacitor electrodes. CV curves for samples annealed at 450 °C for 1 hour are shown in Figure 2.6. The

large shift (-4.9 V) to negative voltages in the control sample was caused by positive Cu ions diffusing into the silica insulator.<sup>8</sup> On the other hand, the silica protected by  $MnSi_xO_y$  only showed a very small shift (-0.1 V). This electrical test is more sensitive to diffusion of small amounts of copper than the other tests. These CV curves also demonstrate that the capacitance of the SiO<sub>2</sub> is not changed significantly by the CVD treatment. Thus, this process should be compatible with recent developments in low-*k* integration.

Figure 2.6 CV curves of samples before and after annealing at 400  $^{\circ}$ C (a) with SiO<sub>2</sub>, and (b) with CVD MnSi<sub>x</sub>O<sub>y</sub> on SiO<sub>2</sub>

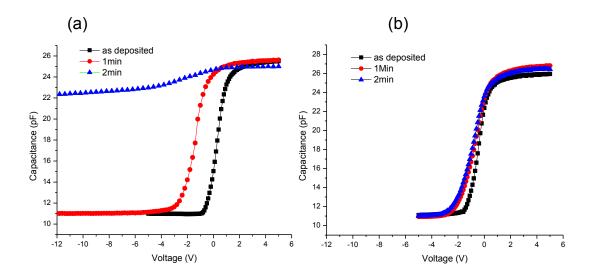

Anneals of similar capacitors were also conducted under an applied voltage of 1 MV/cm at 250 °C. Bias temperature stress (BTS) test is a more sensitive method for detection of copper

diffusion into SiO<sub>2</sub> because ion diffusion is accelerated by an electric field.<sup>8</sup> BTS condition is closer to the environment of chip operation. The control sample lost its capacitance behavior just after 2 minutes under the BTS condition, implying that a large amount of copper had diffused into the Si and the Si would no longer work as a semiconductor. In contrast, the CVD Mn-treated sample had no significant change in its CV curve (Figure 2.7). The BTS test results confirm the superior barrier properties of the MnSi<sub>x</sub>O<sub>y</sub> layers.

Figure 2.7 CV curves of samples before and after annealing at 250  $^{\circ}$ C under a 1 MV/cm field (a) with SiO<sub>2</sub>, and (b) with CVD MnSi<sub>x</sub>O<sub>y</sub> on SiO<sub>2</sub>

#### **Oxygen Barrier Tests**

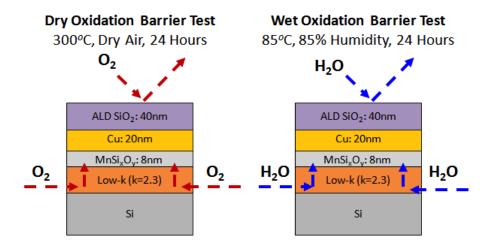

The MnSi<sub>x</sub>O<sub>y</sub> layers were also found to be excellent barriers to oxygen and water. To test oxygen barrier properties of the manganese silicate layers, commercial low-*k* porous insulator layers from Applied Materials were coated with 8 nm of manganese silicate using methods described above, followed by 20 nm of PVD copper. The top surface of the copper was protected with 40 nm of ALD silica.<sup>9</sup> The sample was cut into pieces to expose the edges of the low-*k*

insulator so that oxygen or water vapor could diffuse into the low-*k* layer by the pathways shown in Figure 2.8.

Figure 2.8 structures and pathways for tests of MnSi<sub>x</sub>O<sub>y</sub> as an oxidation barrier

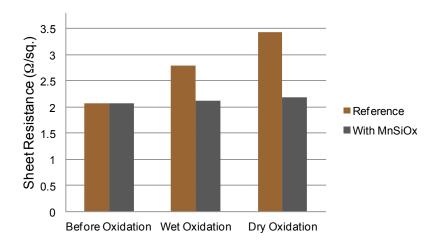

Figure 2.9 Sheet resistance of copper before and after oxidation

After exposure to dry air at 300 °C for 24 hours, the CVD Mn-treated sample maintained its shiny copper color. A control sample without the CVD manganese treatment was corroded near its edges to dark copper oxide by the same exposure. This test shows that the manganese silicate layer is a good barrier to oxygen. Similar tests in a humid atmosphere (85% humidity at 85 °C for 24 hours) showed that the manganese silicate layer is a good barrier to water vapor. These exposures to water and oxygen also significantly increased the sheet resistance of the unprotected control copper layers, whereas the resistance of the Mn-protected copper layers remained nearly constant (Figure 2.9).

#### **Adhesion Enhancement**

The formation of the  $MnSi_xO_y$  layer remarkably increased the adhesion of the Cu/SiO<sub>2</sub> interface, which failed the tape adhesion test prior to the CVD of manganese but easily passed after the CVD treatment. Adhesion strength was quantitatively measured by 4-point bend tests.<sup>10</sup> The samples were prepared by depositing manganese onto thermal SiO<sub>2</sub> on silicon wafers. CVD was used to form copper oxynitride (CuON) at 160 °C. CuON was then reduced to Cu metal by hydrogen plasma at room temperature.<sup>11</sup> The adhesion energy was found to be  $10 \pm 1$  J m<sup>-2</sup>, which exceeds the value of 5 J m<sup>-2</sup> that is considered to be sufficient for making durable interconnections.<sup>12</sup>

The CVD manganese process can also be used to strengthen the adhesion between copper and SiCNOH, a commonly used capping layer. To test the effect of adhesion enhancement, 50 nm of copper was evaporated onto SiCNOH layers (BLoK<sup>TM</sup>, Applied Materials). The Cu showed very poor adhesion, with adhesion energy less than 3 J m<sup>-2</sup>. A similar Cu/SiCNOH layers were treated by CVD of Mn at 350 °C for 10 minutes. This process increased the sheet resistance from 0.5 ohms/square to 1 ohm per square because of the addition of manganese impurity in the copper. The structure was then annealed at 400 °C for 1 hour in a nitrogen atmosphere. The sheet resistance returned to 0.5 ohms per square because the manganese diffused to the surfaces or the interface. The out-diffusion of the manganese from the copper film was confirmed by SIMS analysis. After the manganese treatment, the adhesion energy was increased remarkably to values greater than 12 J m<sup>-2</sup>, because manganese diffused to the interface and formed an interfacial layer. XPS confirmed the presence of manganese at both surfaces created by delamination of the 4point bend test sample.

This manganese metal diffusion process could be used to strengthen the bond between copper and the SiCNOH capping layers. To do this, CVD of Mn could be applied just after chemical-mechanical polishing (CMP), thereby dissolving manganese into the upper portions of the copper below its polished surface. After SiCNOH deposition, the dissolved manganese would diffuse up to the surface of the SiCNOH and strengthen its bonding to copper, which could probably increase the electromigration lifetime of the interconnects.

Because the MnSi<sub>x</sub>O<sub>y</sub> layers are too thin to be imaged by SEM, the distribution of CVD MnSi<sub>x</sub>O<sub>y</sub> was tested by EDX for Mn. The substrates were holes in silicon with an aspect ratio of 52:1 and a native oxide surface with which the manganese precursor reacted. The amount of manganese at the bottom of the hole was 18% of the amount at the top entrance to the hole. This result shows that the manganese precursor has a fairly slow reaction with silica surfaces at 350 °C. As a result, interconnect trenches and vias with typical aspect ratios less than 5:1 can be coated fairly uniformly with CVD MnSi<sub>x</sub>O<sub>y</sub> at 350 °C. At lower temperatures, the surface reactions are expected to be slower, and the conformality should be even higher. Even when roughness is present on sidewalls, the CVD process should form a complete MnSi<sub>x</sub>O<sub>y</sub> diffusion barrier without pinholes or gaps.

#### 2.4 Conclusions

A simple CVD method is presented to make conformal self-aligned diffusion barriers of manganese silicate. This  $MnSi_xO_y$  layer is an effective barrier to diffusion of copper, oxygen and water. Because the  $MnSi_xO_y$  is formed within the insulator, it does not decrease the volume

available for copper, as happens with conventional Ta/TaN barriers. Also, the CVD Mn dissolves into copper surfaces, such as at the tops of vias, so no resistive barrier exists between the tops of vias and the copper in the next higher level. The CVD process can also be used to strengthen the interfacial bonding between copper and a capping barrier layer of SiCNOH. Thus, more conductive and more durable interconnections are possible using the self-aligned MnSi<sub>x</sub>O<sub>y</sub> barriers. The CVD Mn-CuON process should allow formation of conformal seed layers for void-free electroplating of copper in even the narrowest interconnects.

## References

- <sup>1</sup> The International Technology Roadmap for Semiconductors, http://public.itrs.net (2007).

- <sup>2</sup> J. Koike and M. Wada, *Appl. Phys. Lett.*, **87**, 041911 (2005).

- <sup>3</sup> M. Haneda, J. Iijima, and J. Koike, *Appl. Phys. Lett.*, **90**, 252107 (2007).

- <sup>4</sup> T. Usui, H. Nasu, S. Takahashi, N. Shimizu, T. Nishikawa, M. Yoshimaru, H. Shibata, M. Wada, and J. Koike, *IEEE Trans. Electron Devices*, **53**, 2492 (2006).

- <sup>5</sup> J. Iijima, M. Haneda, and J. Koike, *IEEE Int. Interconnect Technol. Conf., Proc.*, 155 (2006).

- <sup>6</sup> B. Lim, A. Rahtu, J. Park, and R. Gordon, *Inorg. Chem.*, **42**, 7951 (2003).

- <sup>7</sup> D. Hausmann, E. Kim, J. Becker, and R. Gordon, *Chem. Mater.* 14, 4350 (2002).

- <sup>8</sup> A. Loke, C. Ryu, C. Yue, J. Cho, and S. Wong, *IEEE Elec. Device Lett.*, 17, 549 (1996).

- <sup>9</sup> D. Hausmann, J. Becker, S. Wang, and R. Gordon, *Science*, **298**, 402 (2002).

- <sup>10</sup> Y. Lin, J. Vlassak, T. Tsui, and A. McKerrow, *Materials Research Society Symposium Proceedings*, **795**, 93 (2004).

- <sup>11</sup> H. Kim, H. Bhandari, S. Xu, and R. Gordon, J. Electrochem. Soc., 155, H496 (2008).

- <sup>12</sup> L. Peters, *Semiconductor International* (July 1, 2001).

## Chapter 3

# Selective Chemical Vapor Deposition (CVD) of Manganese Capping Layer

## **3.1 Introduction**

The power of computers has increased exponentially. This technological feat has been enabled by the fact that transistors improve their performance as they are scaled to smaller and smaller sizes. On the other hand, the endurance of the copper (Cu) wires that connect the transistors becomes poorer as their size is reduced. Until now, the performance of the copper wires has been sufficient to meet the industry standard lifetime of ten years. As the size of the wires is projected to become still smaller, their operational lifetime before failure would become too small.<sup>1</sup>

The fundamental problem is that copper metal forms rather weak bonds to metal oxides and nitrides. Adhesive tape is usually sufficient to remove copper films from these surfaces. Quantitative measurements of debonding energy by the 4-point bend test usually give values less than 1 J m<sup>-2</sup>. This poor adhesion between copper and silicon nitride leads to the most common failure mechanisms of copper interconnects in integrated circuits. An open circuit can form when a copper line breaks after an electric current drives copper along the weak interface between copper and an overlying silicon nitride layer. Short circuits between neighboring lines can also form after this electromigration process extrudes copper from the channels in which it lies.<sup>2</sup>

Placing a metal such as cobalt on the top surface of the copper lines increases the lifetime before failure by electromigration. Cobalt (Co) or cobalt alloys with tungsten and phosphorus or

boron have been placed on copper lines by electroless plating.<sup>3</sup> However, avoiding some metal plating on adjacent insulator surfaces has been difficult to achieve, resulting in higher leakage and/or short circuits between lines. CVD has also been used to deposit Co on Cu lines, but some Co is also deposited on the insulator surfaces, potentially reducing reliability because cobalt on the dielectric can increase leakage and lower breakdown voltage.<sup>4</sup> Cobalt also diffuses from the capping layer into the Cu, increasing its resistance,<sup>5</sup> while manganese can be removed from the Cu by annealing.<sup>6</sup> Selective CVD of ruthenium (Ru) has also been used as a capping layer to increase the lifetime, but some Ru metal is still deposited on the insulator.<sup>7</sup>

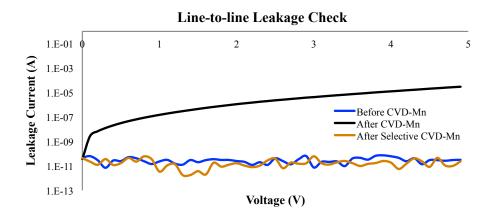

In this chapter, a chemical vapor deposition process is presented to selectively deposit manganese on the desired surfaces of copper wires, while completely avoiding any deposition of manganese on insulators between the copper wires. Gas-phase silylation is essential to achieving this high degree of selectivity, presumably by replacing reactive SiOH groups on the insulator surface with inert SiCH<sub>3</sub> bonds. Manganese metal also dramatically strengthens the interface between copper and silicon nitride, as well as between copper and silicon oxide and low-*k* dielectrics. The debonding energy is found to increase nearly linearly with manganese content at the interface, up to values so large that the interfaces could not be broken apart. Increased adhesion strength has been linked to increased electromigration lifetime.<sup>8</sup> The remarkably high diffusion constant of manganese in polycrystalline copper at 300 °C is evaluated to understand the distribution of manganese in the samples prepared for the study of adhesion. This selective CVD Mn process should allow the construction of multilevel interconnects with longer lifetime and higher speed than previously possible.

### **3.2 Experiments**

#### **Structure of Samples for Measurements**

Substrates for various measurements are shown schematically in Figure 3.1. They include blanket films of thermal SiO<sub>2</sub> on Si, plasma-deposited SiO<sub>2</sub> on Si, CVD Si<sub>3</sub>N<sub>4</sub> on Si, SiCOH low-*k* insulator (BDII<sup>TM</sup>, k = 2.5, from Applied Materials) on Si, and SiCNOH capping barrier and etch-stop (BLoK<sup>TM</sup> from Applied Materials). Thermal oxide and plasma oxide substrates were cleaned of organic contamination by 5 minutes of UV-ozone treatment at room temperature. CVD silicon nitride samples were similarly cleaned by UV ozone, then dipped in dilute HF for one minute, rinsed with distilled water and blown dry. BDII<sup>TM</sup> and BLoK<sup>TM</sup> samples were used as received without any cleaning. Blanket copper substrates were either evaporated or sputtered onto thermally oxidized silicon wafers. A layer of titanium was sputtered prior to the copper in order to provide stronger adhesion to the sputtered copper films. The copper substrates were loaded into the CVD reactor after only a few minutes of air break, so they were fairly clean, except for a thin layer of native oxide.

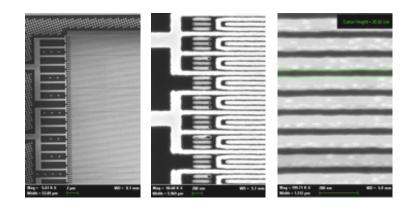

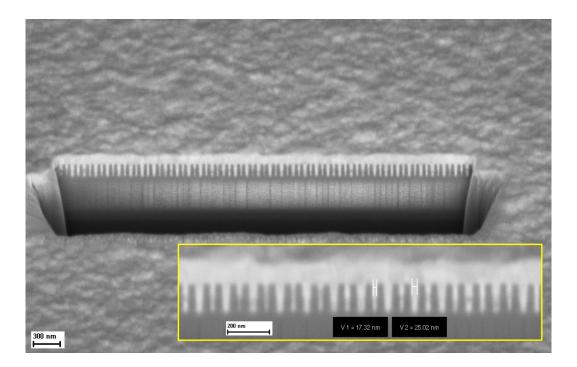

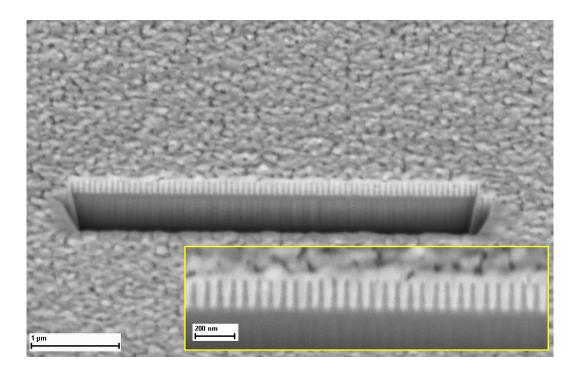

Patterned substrates with interdigitated comb structures were supplied by IBM and by SELETE. These substrates have copper lines up to 10 meters long with 50, 70 or 100 nm copper linewidths separated by dense SiCOH insulators with the same linewidths. These substrates had received a final step of chemical-mechanical polishing (CMP), leaving the copper surfaces covered by a protective layer of benzotriazole (BTA). These patterned substrates were not cleaned prior to use.

| CVD Mn                   | CVD Mn                                                           |                                                              |

|--------------------------|------------------------------------------------------------------|--------------------------------------------------------------|

| PVD Cu                   | PECVD SiO <sub>2</sub> or SiCOH                                  |                                                              |

| PVD Ti                   | Si                                                               | Si                                                           |

| Thermal SiO <sub>2</sub> | (b)                                                              | 51                                                           |

|                          | (~)                                                              | Ероху                                                        |

| Si                       | Si                                                               | PVD AI                                                       |

| (a)                      | Ероху                                                            | PECVD Si <sub>3</sub> N <sub>4</sub> or ALD SiO <sub>2</sub> |

|                          | PVD AI                                                           | CVD Cu                                                       |

| CVD Cu                   | CVD Cu                                                           | CVD Mn                                                       |

| CVD Mn                   | CVD Mn                                                           | PVD Cu                                                       |

| CVD Cu                   | CVD Cu                                                           | PVD Ti                                                       |

| Thermal SiO <sub>2</sub> | SiO <sub>2</sub> , SiCOH, SiCNOH, Si <sub>3</sub> N <sub>4</sub> | SiO <sub>2</sub>                                             |

| Si                       | Si                                                               | Si                                                           |

| (c)                      | (d)                                                              | (e)                                                          |

Figure 3.1 Structures of samples for measuring CVD manganese (a) deposition rate and diffusion rate, (b) SIMS depth profile, (c) selectivity, (d) purity, (e) adhesion to substrates, and (f) adhesion to superstrates.

### **CVD of Manganese and Copper**

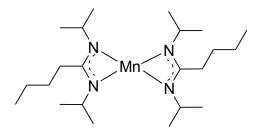

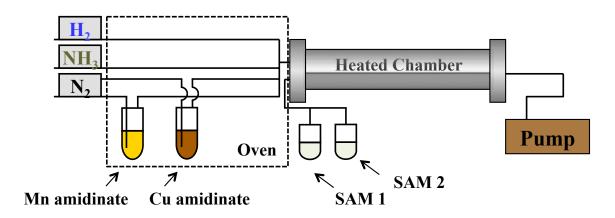

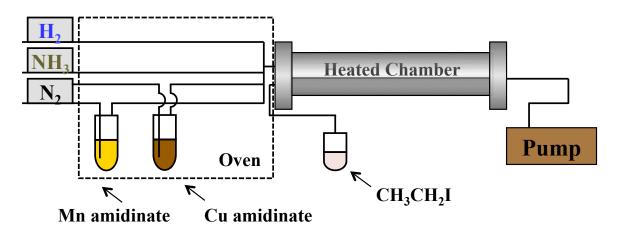

The compound that serves as a precursor for manganese is called bis(N,N'-diisopropylpentanamidinato) manganese(II), whose chemical formula is shown in Figure 3.2. The compound was synthesized by methods similar to those used for other metal amidinates.<sup>9</sup> The vapor pressure of the precursor is estimated to be around 0.1 mbar at 90 °C. For the CVD experiments, the manganese precursor was evaporated from the liquid in a bubbler at a temperature of 90 °C into a 60 sccm flow of highly purified nitrogen (concentrations of water and oxygen less than  $10^{-9}$  of the N<sub>2</sub>). This vapor mixture was mixed with 60 sccm of purified hydrogen at a tee just prior to entering one end of a tubular reactor. The reactor tube has an inner diameter of 36 mm. A half cylinder of aluminum supports the substrates inside the reactor. For most depositions of manganese, the reactor temperature was controlled at 300 °C. The pressure in the reactor was maintained at 5 Torr by a pressure sensor controlling a butterfly valve between the reactor and the vacuum pump.

Figure 3.2 Formula for the manganese precursor

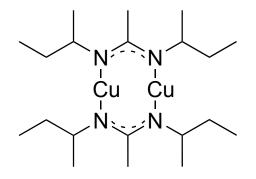

CVD copper was deposited in the same reactor using copper (N,N-di-*sec*-butylacetamidinate) dimer<sup>10</sup> as a copper precursor maintained as a liquid in a bubbler at 130 °C through which 40 sccm of pure nitrogen flowed. 40 sccm of hydrogen was mixed with the copper precursor vapor just before entering the reactor held at a temperature of 200 °C and a pressure of 5 Torr. About 30 nm of copper deposited in 5 minutes under these conditions.

Figure 3.3 Schematic diagram of the CVD system

After the substrates were loaded into the reactor they were flushed with purified nitrogen while they were heated to 200 °C for ½ hour and 350 °C for ¼ hour in flowing purified nitrogen at 1 Torr. During this anneal water was desorbed from the dielectrics and the BTA was evaporated from the copper. Next the native oxide on the copper surfaces was reduced in flowing purified hydrogen gas at 1 Torr for 1 hour at 250 °C. In some runs, manganese was

deposited at this point. In most runs, two silylation vapor pretreatments were applied before the manganese deposition.<sup>11,12</sup> Prior to the silylation treatments, the reactor was cooled to room temperature, pumped down to the base pressure (about 20 mTorr), and then filled with vapor (about 14 Torr) from a room-temperature source of bis(N,N-dimethylamino) dimethylsilane, (CH<sub>3</sub>)<sub>2</sub>Si(N(CH<sub>3</sub>)<sub>2</sub>)<sub>2</sub> (Figure 3.4a), and heated to 90 °C for  $\frac{1}{2}$  hour. Then the reactor was again pumped to base pressure, cooled to room temperature and refilled with the vapor (about 75 Torr) of (N,N-dimethylamino) trimethylsilane, (CH<sub>3</sub>)<sub>3</sub>SiN(CH<sub>3</sub>)<sub>2</sub> (Figure 3.4b), and heated to 90 °C for  $\frac{1}{2}$  hour. After the vapor exposures, the reactor was pumped to base pressure and the samples were then heated to the deposition temperature (typically 300 °C for manganese or 200 °C for copper).

(a) (b)

$$CH_3$$

$CH_3$

$(H_3C)_2N-Si-CH_3$   $H_3C-Si-CH_3$

$N(CH_3)_2$   $N(CH_3)_2$

Figure 3.4 Formula for (a) bis(N,N-dimethylamino) dimethylsilane and (b) (N,N-dimethylamino) trimethylsilane

After the temperature was stabilized, a CVD vapor mixture was passed through the reactor for a time, typically 30 minutes. Some depositions were just manganese, while other runs deposited copper, then manganese and then a second copper deposition, to make Cu/Mn/Cu sandwich structures.

#### **Characterization Methods**

Samples for measuring adhesion of Cu/Mn/Cu to the substrate by the 4-point bend method<sup>13,14,15</sup> were taken through an air break into a chamber in which they received 0.13  $\mu$ m of sputtered aluminum, and then they were attached by high-strength epoxy (EPO-TEK 353ND

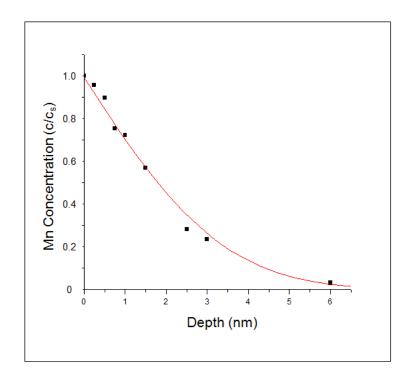

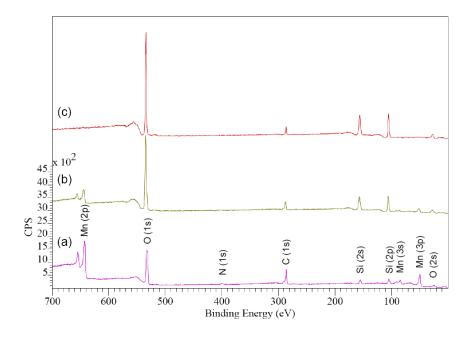

from Epoxy Technology) to a piece of a second silicon wafer. The bonded wafers were cut into  $50 \times 6$  mm beams. A notch was scribed at the center on one of the substrates to initiate the crack. Samples for testing adhesion of copper-manganese to a superstrate silicon nitride layer received an additional PECVD Si<sub>3</sub>N<sub>4</sub> or ALD SiO<sub>2</sub> coating before the sputtered aluminum.